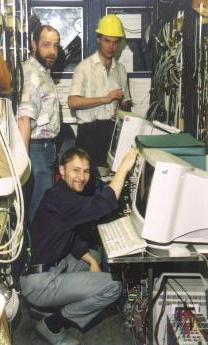

"Development of the repeater card,

the store card and the master card."

|

A number of standard VME modules: two repeater cards, one additional store card and the master card were designed and manufactured as an interface between the BST and the H1 central trigger system. Repeater cards untie high density cables coming from the detector, adapt signal levels to the H1 standard, provide the data fanout, distribute the HERA clock frequency and H1 control signals all over the BSTT and prepare the "front end ready" (FER) acknowledge. There are four rotary switches foreseen on every repeater board. One of these switches is dedicated to the HERA clock frequency delay. The maximum delay amounts to 96 ns - the width of one HERA bunch crossing. Another three switches are used to shift within one clock period the leading and the trailing edges of the "PEN" signal and the data strobe for the master card. Their delay values are biased by settings of the first switch. A special algorithm implemented into the "ACEX" EP1K30 chip requires a single delay line for the global phase steering. In a test mode these cards emulate the "PEN" and the "Fast Clear" signals on their own. The toplogical data from the front-end is kept in the H1 standard PQZP system. On demand of the central DAQ this data is passed to the second-level topological trigger (L2TT). A PQZP extension unit, the so-called "store card", was designed to supervise the raw data transmission to the L2 |

|

neural network trigger (L2NN). For every H1 event the raw and the topological BSTT data could be read out via the "VMEtaxi" VME-controller and then written onto the tape in the TSCD trigger bank. The master card unifies data streams from 6 motherboards and provides the L1 trigger or veto decision. In addition, it appends the BSTT status word to the TSCD trigger bank. The "read" and "write" functions on the VME bus were programmed for the standard (A24) supervisory and non-privileged data access. The firmware was compiled in the "Quartus" development system with the entry code prepared in the VHDL. |