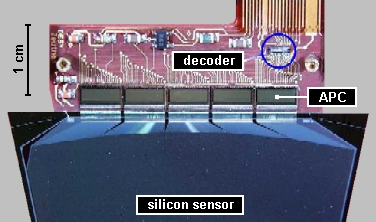

"Semi-automatic setup for ASIC tests."

|

For about 300 new R- and Phi-strip hybrids were necessary

to build up the BST-2000 and FST devices. Each hybrid is

equipped with a silicon R-strip or Phi-strip detector, 5 analog

pipeline chips APC-128 SAC1 PSI 19 (APC) and one decoder chip

SAC1 PSI 21. Thus the total number of integrated circuits (IC)

to be assembled amounts to 1800 pieces. Only perfect APCs with

small tolerance in their parameters have to be used to avoid any

detector failures during their operation. In foundry, the yield

of faultless ASICs (application-specific integrated circuits) is

less than 100%. In order to make the chip test fast and efficient

a special semi-automatic system was developed. This was a part of

the BST "strip" system combined with a "Wentworth Laboratories"

IC-manipulator. The software for the VME interface and for the

online data analysis was written in the "LabView 5.0" and it was

running under the "MacOS 8.0" operating system.

The APC response to the input calibration pulse was studied

in order to prove the IC quality. The chip contains 128 individual

channels; every channel has an analog memory for 32 amplitudes.

Thus 4096 structures were measured and classified at once according

to their amplitude dispersion. About 75% ICs of the high quality

were accepted from the whole delivery. Else 13% were specified as

"good" samples and the rest was refused.

On the same experimental platform there was a new experiment

assembled for SAC1 PSI 21 decoder tests. Since this is a fully

digital device for which the only functionality matters, its

positive outcome was nearly 100%.

When the ageing effects in the BST and the FST front-end arose I have redesigned the APC chip and its decoder in the mixed-signal UMC 0.25 um process (IBM compatible) using the "radiation-tolerant" libraries (up to 50 MRad) developed by the Paul-Scherrer Institute in Switzerland. The yield of high quality APCs was 50%, most of rejected chips stemmed from the wafer's boundary area. There were no faulty decoders detected.