### SiLC Test beams

Zdeněk Dolezal Charles University Prague

### Beams available

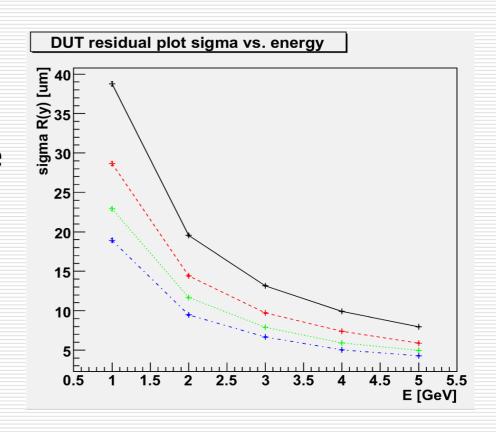

- □ DESY, 1-6 GeV e

- Good access via EUDET

- Problem of multiple scattering (track precision >10 μm)

- G4 simulation (Prague)

- Sep 18-22 booked

### Beams available

- $\square$  CERN, 20-200 GeV  $\pi,\mu,e$

- High quality beam

- Helsinki participate in TOTEM, possibility to run in a piggyback mode

- Schedule for 2006 unsure due to recent magnet failure

- FNAL:

- beam structure not very convenient

- ☐ SLAC

### SiTRA-JRA2 Roadmap

From 18/9/06 to end 06 DESY 5 GeV ebeam, S/N with: 180nm chip, medium & long strips ladder

Fall'07: FNAL (CERN)

First combined tests

(small calo, and TPC)

within B field

with Si prototypes

and 128 ch chips

Spring'09:

FNAL(CERN)

Combined test with

final protos of Si

tracker, calo and TPC,

within B field

new foundry FE chips,

cooling and alignment

protos

2006

2007

2008

2009

Preparation test beam 07: 128ch chips & detector protos

Preparation test beam 09: new chips & new detector protos, cooling & alignment

### DESY September 2006

From 18/9/06 to end 06 DESY 5 GeV ebeam, S/N with: 180nm chip, medium & long strips ladder

#### Test Beam at DESY in 2006 2.Half Responsible August October November Collaboration/Sub-invascular | 03 | 10 | 17 | 24 | 31 | 07 | 14 | 21 | 28 | 04 | 11 | 18 | 25 | 02 | 09 | 16 | 23 | 30 | 06 | 13 | 20 | 27 | 04 Stahl et.al. 22 ILC/E166 Bruschi ATLAS/Luminometer Savoy-Navarro 22 22 SHUTDOWN NO BEAM

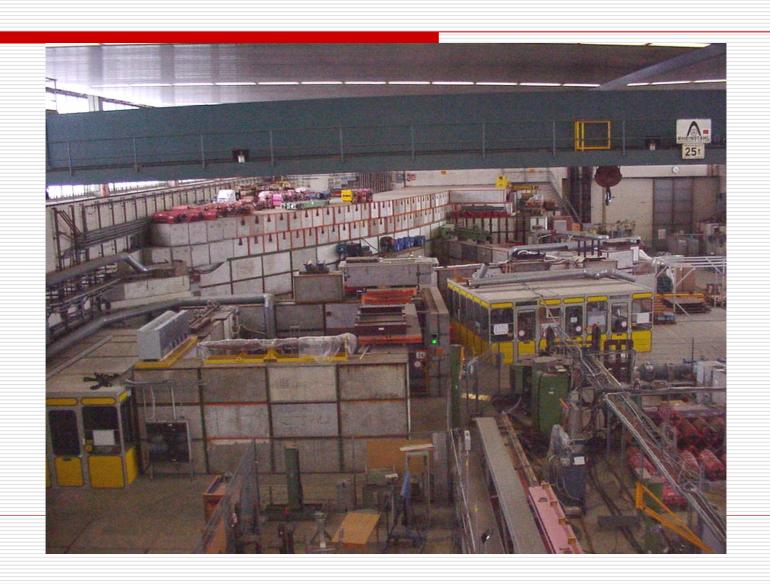

## **DESY Beam Area**

### What is needed?

- ☐ Trigger + DAQ + Telescopes

- Prototype modules + DAQ HW

- DAQ software

- Chamber, XY stage

- Manpower (experts, shifters)

- Data analysis

## Trigger + DAQ+Telescopes

#### **ZEUS DESY group telescopes booked:**

#### trigger photomuliplier

3 defining an area of 9x9 mm2 triggering the readout of the 3 telescope units

#### telescope

3 modules with crossed sensors about 3x3 cm2; diode pitch 25 micron, readout pitch 50 micron ("Cern type", Coledani et al., <u>NIM372(1996)379</u>)

#### readout

CAEN module 550 and 551 in VME Power PC in the VME crate coincidence, deadtime control,... in a NIM crate in the hut. The VME crate is close to the telescope. Software and data format under investigations

## SiLC Prototype Modules

#### 30 cm ladders

- 2 new ladders with 3 9-cm CMS sensors each, i.e. 28 cm strip length one equipped with VA1 chips (for a comparison) and the other with SiLC UMC 180 nm chip

- This module will be built in Paris

### Long ladder

- a new prototype with 10 GLAST sensors, i.e. 90 cm strip length equipped with SiLC UMC 180 nm chip

- This module will be built in Karlsruhe and populated with chips probably in Paris

- Option with 2 readout chips (UMC+VA) exists

### DAQ HW+SW

#### Telescopes:

- CAEN VME V550+551 ADC+sequencer

- PowerPC in VME Crate, Lynx OS

- DESY Support promised

#### SiLC modules:

- Interface card between UMC/VA chips and ADC

- NI AD card, 100 MHz, 14 bit (PCI or PXI)

- LabView DAQ SW tested in lab in Paris

- Readout speed limitations

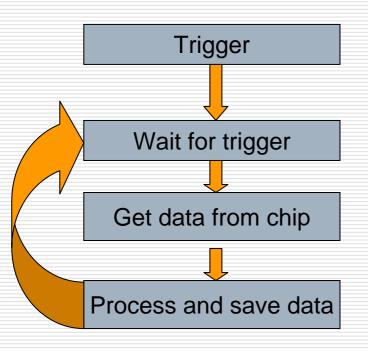

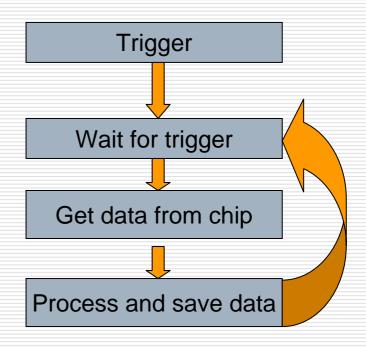

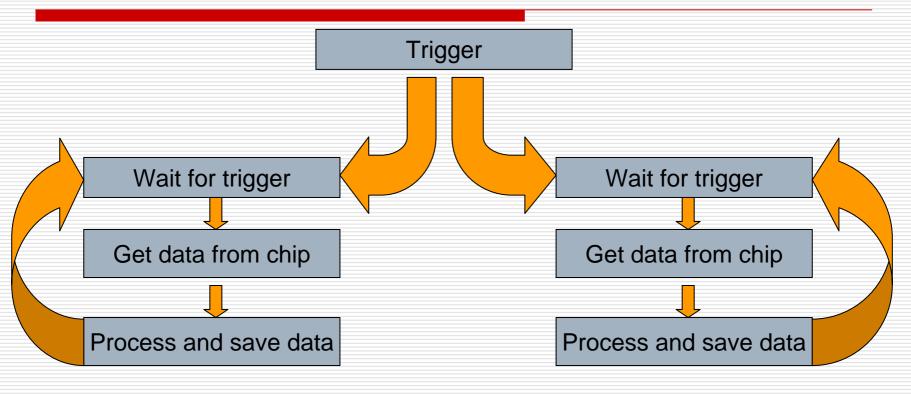

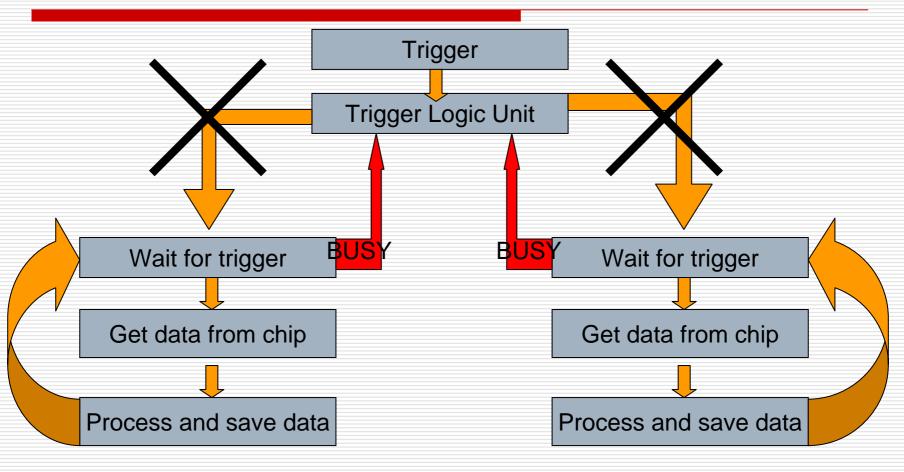

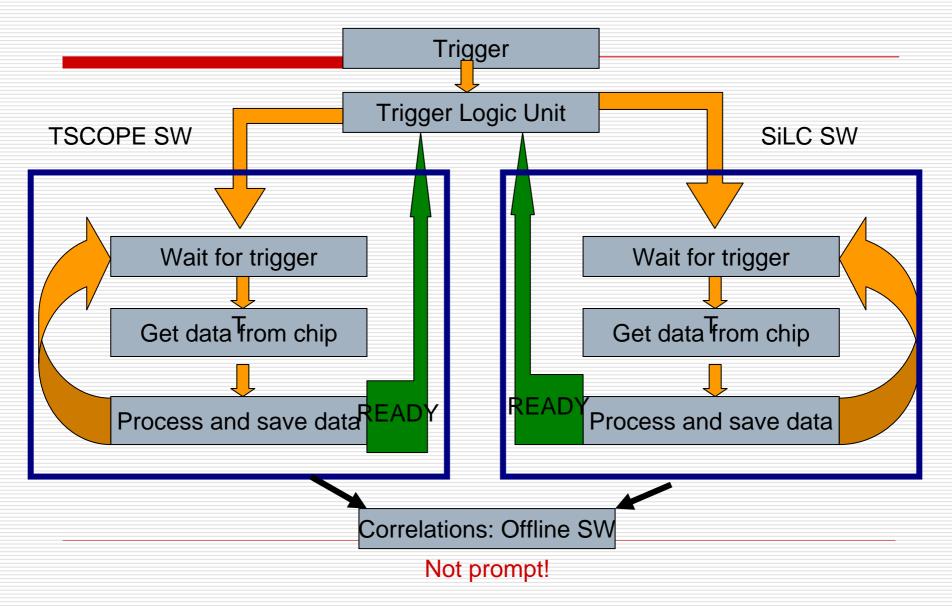

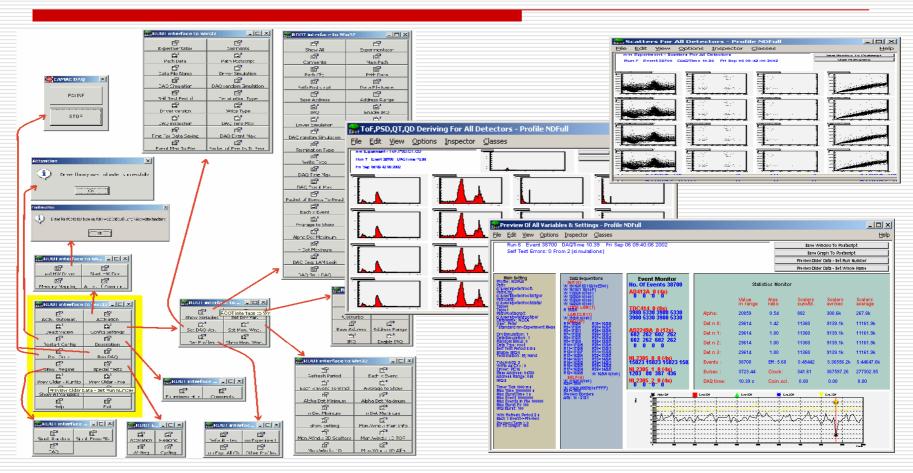

### Standalone Telescope+Proto DAQ

Telescopes VME PowerPC readout, Lynx

SiLC NI AD card (PCI or PXI), LabView DAQ SW

Synchronisation might be time consuming!

Hard to test in advance, but need to be prepared:

- data formats

- readout logic

- source codes

VME, Power PC, Lynx OS

NI scope card, PCI/PXI, Windows, LabView

- □ Hardware?

- Operating system?

- SW Platform?

- ☐ Perspective?

#### Operating system?

- Telescopes: VME can be read with a different communication board (NI PCI-VME) under Win or Linux

- ☐ SiLC

- No need to leave Windows

### SW platform?

- LabView: 'easy', but slow

- □ Windows MSVC++: fast, can use dll from vendors for PCI/PXI,VME + ROOT GUI + plots

### Perspective?

- ☐ Telescopes:

- The same for DESY beams

- Hopefully similar or identical for CERN/FNAL beams

- New EUDET for 2008+ with common DAQ?

- ☐ SiLC

- R/O mode change with 130 nm (end of 2006): digital readout

- Simpler DAQ HW will be needed

- Keeping SW/HW functionality for 180 nm/VA desirable for crosscheck

#### Proposal

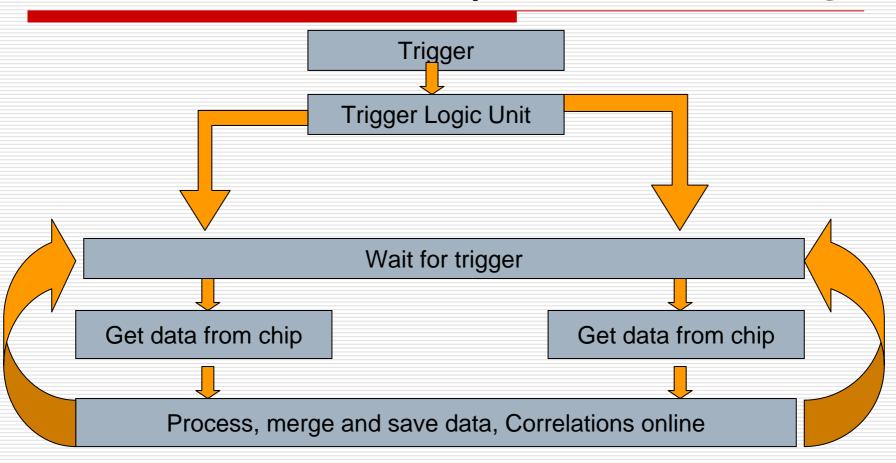

- □ September 2006: stay with 2 standalone synchronised systems

- □ 130 nm (end of 2006): attempt to create common TB software

#### Who?

- □ Prague: MSVC++ + ROOT,

- Other proposals, participations

- Prerequisites: all info on communication protocols, chip configuration sequences, etc.

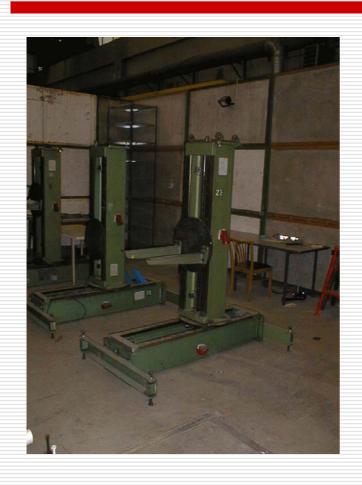

## Chamber, supports, XY stage

- Concrete blocks, tripod available on site

- 30 and 1000 kg XY stages with a remote control exist at DESY

- 30 kg XY stage booked

- Chambers?

- Dry nitrogen: to be checked

# Chamber, supports, XY stage

## Responsibilities

- Telescopes, trigger...

- Prague

- Obninsk

- DESY

- Prototypes+ test setup

- Paris

- □ Karlsruhe

- Mechanics, chambers

- Obninsk

- DESY

- Paris

- Karlsruhe

- Readout

- Prague

- Paris

- DESY

- Offline analysis

- Prague

- Shifts

- ☐ All (who?)

- Data analysis

- Prague

- Everyone interested

SiLC test beam page: www-ucjf.troja.mff.cuni.cz/ilc