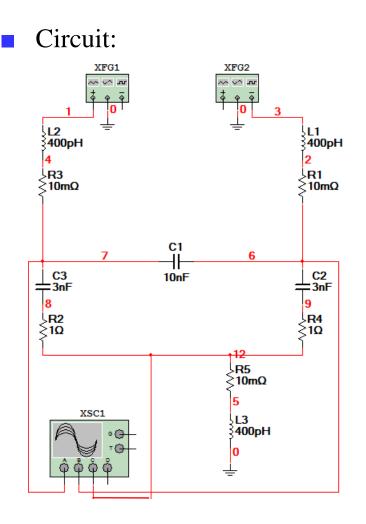

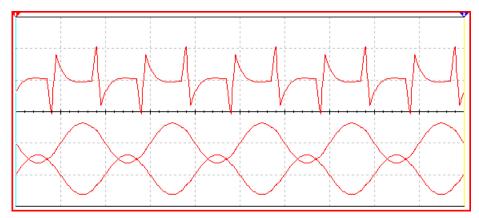

## Substrate bounce – multiple wire bonds

Phase 1 and 2 square, 1 V<sub>pp</sub>, 50 MHz, 1 ns/2 ns rise times:

- Phases 1 and 2 (lower two traces) both 10V/div.

- Substrate bounce (upper trace)

200 mV per division.

- Bounce voltage  $\pm 40 \text{ mV}$  for 2 V<sub>PP</sub> gate voltage.

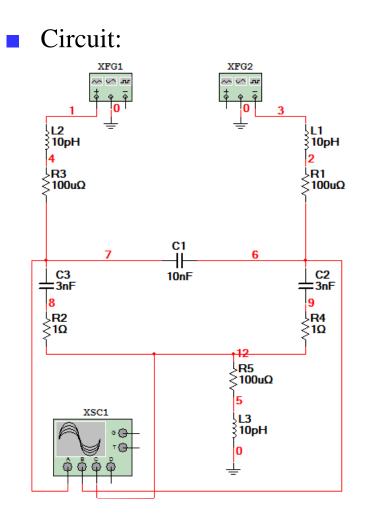

## Substrate bounce – multiple bump bonds

Phase 1 and 2 square,  $1 V_{pp}$ , 50 MHz, 1 ns/2 ns rise times:

- Phases 1 and 2 (lower two traces) both 10V/div.

- Substrate bounce (upper trace)

20 mV per division.

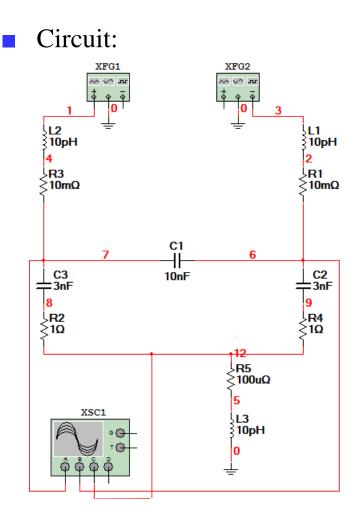

## Multiple bump bonds take two

Phase 1 and 2 square,  $1 V_{pp}$ , 50 MHz, 1 ns/2 ns rise times:

- Phases 1 and 2 (lower two traces) both 2V/div.

- Substrate bounce (upper trace)

20 mV per division.

- Bounce voltage about ±14 mV for 2 V<sub>PP</sub> gate voltage.

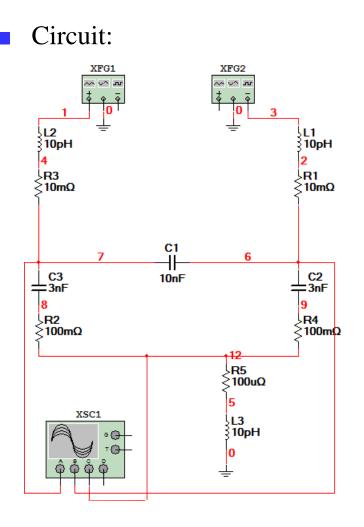

## Effects of "substrate resistance"?

Phase 1 and 2 square, 1 V<sub>pp</sub>, 50 MHz, 1 ns/2 ns rise times:

- Phases 1 and 2 (lower two traces) both 2V/div.

- Substrate bounce (upper trace) 100 mV per division.

- Bounce voltage about ±100 mV for 2 V<sub>PP</sub> gate voltage.