# LCFI Report for the Vertex Detector Review at Fermilab

October 2007

The Universities of Bristol, Edinburgh, Glasgow, Lancaster, Liverpool, Nijmegen, Montenegro and Oxford and the Rutherford Appleton Laboratory

# **Contents**

| LCFI Report for the Vertex Detector Review at Fermilab | 1  |

|--------------------------------------------------------|----|

| Contents                                               | 2  |

| LCFI: Introduction and Scientific Goals                | 4  |

| Introduction                                           | 4  |

| Scientific Motivation                                  | 4  |

| Flavour Identification at the ILC                      | 5  |

| The ILC and Vertex Detector Design                     | 5  |

| The LCFI Programme                                     | 7  |

| Summary                                                | 9  |

| WP1 – Physics Studies                                  | 11 |

| Introduction                                           | 11 |

| Quark charge selection and vertex detector parameters  | 11 |

| The LCFI Vertex Package                                | 13 |

| Future Programme                                       | 14 |

| WP2 – Sensor Design and Production                     | 20 |

| Introduction                                           | 20 |

| Future Programme                                       | 23 |

| WP3 Readout and Drive Electronics                      | 26 |

| Introduction                                           | 26 |

| Future Programme                                       | 28 |

| WP4 – External Electronics                             | 31 |

| Introduction                                           | 31 |

| Future Programme                                       | 33 |

| WP5 – Integration and Testing                          | 35 |

| Introduction                                           | 35 |

| Future Programme                                       | 38 |

| VP6 – Mechanical Studies | . 42 |

|--------------------------|------|

|                          |      |

| Introduction             | .42  |

| Future Programme         | .43  |

| ummary                   | . 48 |

| ·                        |      |

| eferences                | .50  |

# **LCFI: Introduction and Scientific Goals**

## Introduction

This report describes the status of the research programme of the Linear Collider Flavour Identification (LCFI) Collaboration and presents the work the Collaboration proposes to carry out in the period from the end of 2007 until 2012. This represents a continuation of LCFI's current research, with the goal of developing the sensors for the Vertex Detector (VXD) of the International Linear Collider (ILC), the associated mechanical support structures and the necessary ancillary electronics. In addition, the algorithms and software that LCFI has produced for the VXD, allowing its use for quark flavour and charge identification at the ILC, will be further developed and optimised and other uses of the VXD in physics analysis explored. The design of the VXD will be optimised and the associated software tested using Monte Carlo simulations of "benchmark" physics processes, chosen to be particularly sensitive to VXD performance.

The objective of the LCFI group is to ensure that it, with international partners, is in a position to make a major contribution to the construction of one of the ILC VXDs. Once the ILC, with its VXD, is operational, LCFI physicists will participate in physics analysis at the ILC, focussing on the many measurements in which the identification of the flavour and charge of heavy quarks is crucial.

The timescale for the research programme presented here is determined by progress with the design and construction of the ILC. A major step forward was taken when the Reference Design Report (RDR) was published. This is to be followed by an Engineering Design Report (EDR), to be released in 2010, and the detectors for the ILC must be planned on a timescale concomitant with this. Letters of Intent to produce Engineering Design Reports for ILC detectors have been requested, and LCFI foresees contributing to the VXD sections of two detectors concepts, the SiD and the ILD. The detector EDRs will be produced on the same timescale as that for the ILC, and it is hoped that construction of the ILC and its detectors will start in around 2013. The VXD R&D programme outlined here must therefore be completed by 2012.

In the following, a brief description of the motivation for the ILC and for high performance flavour identification is given. The LCFI programme is then summarised. This programme is broken down into Work Packages, which are described in more detail in the latter section of the report. Finally, a summary is given which includes estimates of the resources required to complete the proposed LCFI programme.

## Scientific Motivation

Our current understanding of the fundamental interactions of nature is encapsulated in the Standard Model (SM) of Particle Physics. Aspects of this model remain to be experimentally demonstrated and, despite its many successes, it is clear that the Model is not complete. An example of the former is the Higgs sector, where the Higgs boson has yet to be observed. Examples of the latter are provided by the fact that the SM does not provide an explanation for the observed number of generations of quarks and leptons, nor does it account for the relative strengths of the strong and electroweak interactions: no attempt is made to describe gravitational interactions. New experimental data are needed both to fully understand the SM and to determine which, if any, of the many proposed extensions of this theory are able to provide a more complete description of

nature. These data will be provided by the Large Hadron Collider (LHC), which will commence operation at CERN in 2008 and will collide two proton beams at a centre-of-mass energy of 14 TeV, and by the ILC, which will collide electron and positron beams at a centre-of-mass energy ranging initially from about 90 GeV to 500 GeV; this latter energy will later be increased to 1 TeV.

#### Flavour Identification at the ILC

The examples of the physics to be studied at the ILC given above illustrate a further point of interest: many of the measurements can be greatly enhanced by the identification of the flavour of the heavy c and b quarks produced in the electron-positron collisions at the ILC. The determination of the branching ratios of the Higgs boson's decays to heavy quarks and leptons, assuming that the Higgs is observed at the ILC, requires the identification of b and c quarks and of  $\tau$  leptons. As the cross sections for the Higgs production and decay are small, this flavour identification must be efficient. Even at the ILC, the backgrounds are significant, so high purity must also be achieved. The b and c quarks are identified via their characteristic lifetimes and hence the distances they travel between their production and decay. For these decays, the impact parameters of the decay products are typically of the order of a few 100 µm. Identifying these requires that several space points on the tracks of the b and c decay products be measured with a precision of better than 5 µm within a few centimetres of the production vertex and that this be done with minimal disturbance of the flight paths of those decay particles. The VXD necessary to accomplish this measurement must thus perform significantly better than even the best such detector constructed to date, the VXD3<sup>2</sup> of the SLAC Large Detector (SLD) Collaboration which used Charge-Coupled Devices (CCDs) that were designed and manufactured by e2v technologies.

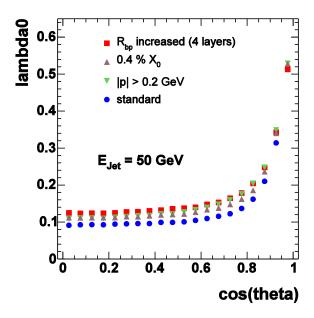

# The ILC and Vertex Detector Design

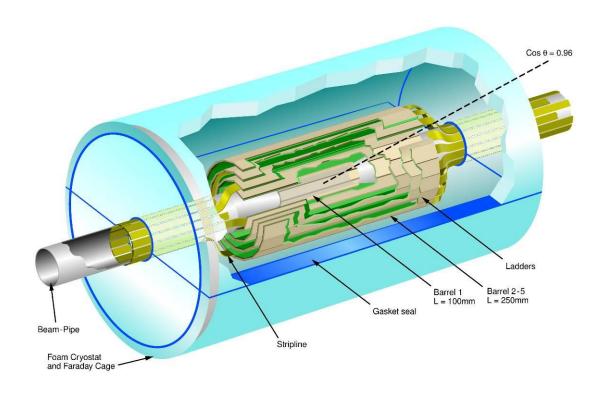

The baseline LCFI VXD is illustrated in Figure 1. As is shown later in this report, it has been demonstrated to be a powerful tool for flavour identification at the ILC. The detector consists of five layers of CCDs with  $20 \times 20~\mu\text{m}^2$  pixels which provide a point resolution of about 3.5  $\mu$ m in both the r $\phi$  direction transverse to the beam-line and the z direction along the beam-line. The sensors are arranged in concentric "barrels" around the beampipe. The innermost layer is at a radius of 1.5 cm and the outermost at 6 cm. In the design shown, the innermost barrel is made up of 8 modules or "ladders", each of which is composed of a sensor of dimensions  $1.3 \times 10~\text{cm}^2$  with readout and other electronics at both ends. The further layers are constructed using up to 20 ladders, each of which is composed of two sensors of dimensions  $2.2 \times 12.5~\text{cm}^2$  with electronics located at the outer ends only. This design results in a total number of pixels of nearly  $10^9$ .

Figure 1 The CCD-based vertex detector design developed and studied by the LCFI Collaboration.

Location of the electronics at the extremes of the polar angle  $\theta$  ensures the amount of material in the central tracking volume is minimised. This is essential, as the momentum of the charged tracks in heavy quark decays at the ILC extends to values as low as a GeV and below, implying that multiple scattering effects must be minimised. The goal is to produce ladders with a thickness of only 0.1%  $X_0$  (c.f. SLD VXD3, 0.4%  $X_0$ ). Minimisation of the material budget also dictates that only gas may be used for cooling the sensors in the sensitive volume of the detector. The sensors must therefore consume at most a few tens of watts of power.

The ILC environment presents many challenges to the designers of vertex detector sensors. For example, at a centre-of-mass energy of  $\sqrt{s}=500\,\text{GeV}$ , trains of about 3000 bunches (or about 5000 at  $\sqrt{s}=1\,\text{TeV}$ ) will pass through the beampipe within the ILC detector at a frequency of approximately 5 Hz. Within these trains, tightly focused electron and positron bunches collide roughly every 350 nanoseconds (about 150 ns at  $\sqrt{s}=1\,\text{TeV}$ ) generating not only the e<sup>+</sup>e<sup>-</sup> interactions of interest but also large numbers of electron-positron pairs which cause background hits in the vertex detector. With pixel sizes of  $20\times20~\mu\text{m}^2$ , in order to ensure that the occupancy in the sensors in the inner layer of the VXD remains below about 1% so track finding is not compromised, the signals in the sensors must be read out or stored about 20 times during the bunch train, or roughly every 50  $\mu\text{s}$ .

A further challenge at the ILC is illustrated by the experience of the SLD vertex detector, the only vertex detector operated in a linear collider environment to date. This detector suffered from beam-induced pickup, caused by the leakage of RF power generated by the wake fields of the passing electron and positron bunches. Fortunately, at SLD, where the time between bunch crossings was 8 ms, it was possible to wait a few hundred microseconds for the electromagnetic interference (EMI) to die out and the electronics to recover before initiating the read out.

# The LCFI Programme

## Sensors for the vertex detector

As is discussed above, the sensors used at the ILC must provide high point precision, good two-track resolution and be extremely thin. It has already been demonstrated that Charge-Coupled Devices (CCDs) can satisfy some of these requirements, for example, the CCDs used in the vertex detector of the SLD experiment achieved hit resolutions of 3.5  $\mu$ m. However, the sequential readout of these CCDs cannot achieve the readout speeds needed at the ILC. This has prompted LCFI to develop, with e2v technologies, Column Parallel CCDs (CPCCDs). Two generations of these devices have now been tested and speeds close to those required at the ILC demonstrated. Devices of a size similar to that required for the VXD have also been manufactured.

One of the major challenges in operating the CPCCD arises from the relatively large intergate capacitance of the device. Achieving the gate voltages necessary to drive charge through the CPCCD requires large currents to charge this capacitance. This is a challenge for the drive circuitry and affects the power dissipation. Although LCFI has designed and tested a chip capable of producing the necessary drive currents, reducing the intergate capacitance remains an attractive goal. Several possible design modifications have been submitted for manufacture that may allow this to be achieved. Similarly, reduction of the dopant induced potential barriers between the pixels of the CPCCD will result in decreased drive voltages and reduced power dissipation. LCFI is pursuing studies with e2v to this end.

A different approach to achieving low occupancies in the inner layers of the VXD is to store hit information locally in the pixels during the ILC bunch train, with readout being performed in the long inter-train gap. LCFI has proposed using a device which uses this technique, the In-situ Storage Image Sensor<sup>3</sup> (ISIS). In the ISIS, small CCD registers in each pixel store the charge released by particle hits. Proof-of-principle devices have been constructed by e2v and successfully tested by LCFI: these sensors are currently being studied in test beams at DESY. There are many advantages to the ISIS approach. For example, a readout speed of a few MHz is quite sufficient. The ISIS will also be more radiation tolerant than the CPCCD due to the reduced number of charge transfers necessary. In addition, the storage of the raw charge associated with the hit makes it possible to design in a high degree of robustness against electromagnetic interference (EMI), the importance of which is illustrated by the SLD experience. If the ISIS is constructed using CMOS technology, it may be possible to make the sensor and readout electronics on the same piece of silicon, reducing the detector mass, especially in the forward region.

The advantages of each of these sensors must be balanced against the challenges that must be overcome before they can be used at the ILC. The primary challenge for the CPCCD development has been the achievement of the necessary readout speed using low-mass drive electronics: significant progress has been made in this area. The ISIS sensors are more attractive than the CPCCD in some respects, for example their radiation hardness, the relaxed readout speed requirement and their resistance to EMI. However, LCFI have yet to incorporate CCD-like storage registers in CMOS devices. LCFI thus propose to pursue the development of both devices to ensure that they have a sensor ready for use at the ILC if the most aggressive timescales are realised, while continuing development of the sensor optimally matched to the conditions at the ILC.

# Simulation of the vertex detector and its physics performance

LCFI has invested considerable effort in the development of tools for using the VXD for flavour and charge identification and in physics studies. The Collaboration's Vertex Package, released early in 2007, provides a comprehensive set of routines for flavour and charge identification at the ILC. LCFI has also performed some VXD optimisation studies, repeatedly emphasized the importance of a small beam pipe radius, for example, which has influenced the design of the ILC interaction region. The Collaboration also presented the first studies of the physics possibilities opened up by the identification of the charge of the b and c quarks at the ILC. It was shown that this is feasible for a large proportion of heavy flavour events by identifying the charges of all the tracks associated with the b and c decay vertices. As the association of tracks to vertices must be correct for all charged particles, even those of lowest momentum, b and c charge identification further sharpens the requirement that multiple scattering in the VXD be minimised.

In the coming years, the Collaboration proposes to continue and extend these studies. Effort will be devoted to refining the heavy flavour identification algorithms and to improving the b and c charge identification provided by our Vertex Package. For example, heavy flavour identification will be improved by including further information on the correlations between the positions of the decay vertices identified in an event, while quark charge identification will be extended to cover cases in which neutral B hadrons are produced by using correlations between the charges associated with the b and c decay vertices.

A further focus of the LCFI studies will be the optimisation of the VXD design. For example, vertex detectors with various sensor layouts will be simulated and the effects on flavour and charge identification investigated. The performance of the detector designs with regard to various benchmark physics processes will also be studied.

LCFI will continue to provide input to international discussions on the possibilities opened up by the addition of new capabilities to the ILC detector. An example here is the question of particle identification. So far this has been thought to be largely irrelevant at the ILC, but the physics gains arising from identification of the charge of b and c quarks are now becoming apparent due to the work of LCFI. Such charge identification can be enhanced by kaon detection, for example<sup>4</sup>.

## **Ancillary electronics**

In addition to the sensors, the VXD requires readout and control electronics for its successful operation. LCFI has designed and produced three generations of column parallel readout chip, which have been bump-bonded to the CPCCDs and successfully tested. The latest of these chips incorporates not only amplification and digitisation circuitry but also cluster finding and data sparsification. Further generations of this chip are planned, culminating in a device that is suitable for the VXD. While this development has been driven by the CPCCD, it is also applicable to the ISIS. Indeed, use with the ISIS is considerably simpler due to the relaxed readout speed of this device.

Particularly challenging is the design of a chip to produce the clock signals for the CPCCDs. Clock voltages of around 2  $V_{PP}$  are needed for efficient charge transfer, and the relatively large intergate capacitance of the current generation of CPCCDs implies that currents of about 20 A are needed to generate these drive voltages. Tests of the first Column Parallel Drive chip designed by LCFI, CPD1,

have shown that this goal has been achieved, provided low inductance connections to the CPCCD can be established. Future tests will involve bump-bonding CPD chips to CPCCDs to realise this.

Of considerable importance for the LCFI R&D programme is the design and construction of the many printed circuit boards and other external electronics systems necessary for the testing of the sensors, the readout chips and the drive circuitry. LCFI has developed an expert electronic engineering support team that has acquired considerable experience in the design of these systems. This team will continue to support the LCFI programme and will contribute to studies of the integration of the sensors, readout and drive chips necessary for the VXD.

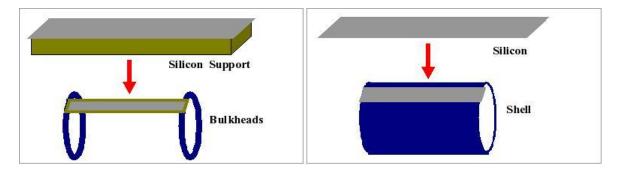

#### **Mechanical studies**

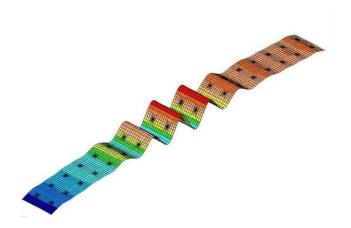

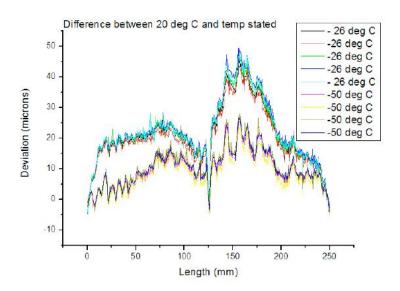

Sensors capable of particle tracking at the few micron level are of little value if they cannot be mechanically supported in a structure whose behaviour is understood to a similar or better level of precision. LCFI has investigated various designs for sensor support, including attaching sensors thinned to about 20  $\mu$ m to a beryllium substrate, an "unsupported" option in which a sensor of thickness about 50  $\mu$ m is held under tension and the use of new materials such as reticulated vitreous carbon (RVC) and silicon carbide foams. The differing coefficients of expansion of silicon and beryllium were shown to make this unsuitable as a substrate, while unsupported silicon sensors were shown to suffer from bowing in the direction transverse to that in which tension was applied. (This arises due to the stresses introduced when the silicon is processed in sensor manufacture.) Both RVC foam/silicon sandwiches and SiC foam as a substrate look to be very promising options for ladder construction. LCFI is further investigating these materials, developing metrology and machining techniques. Studies of VXD designs based on carbon fibre have also started.

A further issue in the construction of the VXD is the need to cool the sensors and electronics. Here, exploitation of the duty cycle of the ILC will allow the heat budget to be kept to a few hundred watts, making cooling using a gentle gas flow feasible. LCFI has constructed a cooling prototype to investigate this possibility and compared the results from the prototype with finite element calculations. Future simulations will study the dynamics of the system introduced, for example, when the CPCCD drive is operated only during the ILC bunch train. This is likely to result in temperature fluctuations: the vertex detector will heat up during the approximately 1 ms long bunch train then cool down in the 0.2 s between bunch trains. The effect of these fluctuations must be understood at the micron level if the detector is to provide the required precision.

# Summary

There is widespread agreement that progress in Particle Physics in the next two decades will best be achieved through the construction of the International Linear e<sup>+</sup>e<sup>-</sup> Collider (ILC) with a centre-of-mass energy ranging between the Z mass and 1 TeV. In this report, the Linear Collider Flavour Identification (LCFI) Collaboration presents a coherent programme of research, the goal of which is to ensure that, with our international partners, LCFI physicists are in a position to contribute to the construction of the vertex detector (VXD) for the ILC. To facilitate the detailed discussion of the programme, six Work Packages (WPs) are defined. These are:

**WP1** This covers simulations of the VXD and the physics studies that must be undertaken in order to optimise the sensors and VXD and guide the designers of the ILC as well as the development of the software tools that are needed to use the VXD.

**WP2** This covers the design and construction of the Column Parallel Charge-Coupled Device (CPCCD), a sensor which has the potential to satisfy the demanding requirements of operation at the ILC, and of the In-situ Storage Image Sensor (ISIS), which may ultimately offer better performance than that of the CPCCD.

**WP3** This Work Package is responsible for the Application Specific Integrated Circuits that must be designed, produced, and tested for the readout of the sensors as well as the chips required to drive the CPCCD.

**WP4** This covers the design and production of the many printed circuit boards (PCBs) and electronics systems needed for the testing of the various sensors in the laboratory and at test beams.

**WP5** This Work Package is responsible for the programme of tests of the various sensor types, including studies of the achievable readout speed and the radiation hardness of the sensors and the testing of sensors in beams.

**WP6** This covers the design of the mechanical support structures for the sensor modules and of the overall vertex detector.

The remainder of this report discusses the results achieved in, and the future programme of, these Work Packages.

# **WP1 - Physics Studies**

## Introduction

The aim of the LCFI physics studies is to guide the design of the VXD by assessing different detector designs, to strengthen the case for the ILC by demonstrating the physics made accessible by the collider and its detectors, and to develop the tools necessary for such studies. Work by the LCFI Collaboration has already contributed to all these areas, demonstrating for example the importance of small beam pipe radius and the physics gains of measuring quark charge. The Collaboration has also expended considerable effort in developing a Vertex Package to exploit the information provided by the VXD. This work is described briefly in the following, as are LCFI's plans for future physics studies

# Quark charge selection and vertex detector parameters

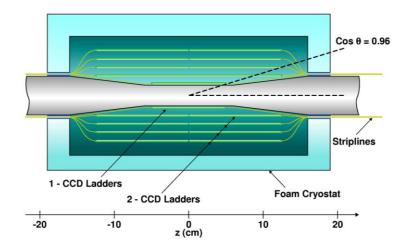

The LCFI group has investigated the possibility of measuring the charge of hadrons containing heavy quarks at the ILC and hence performing quark charge selection. This can be done by assigning all the charged tracks in a jet to a primary, a secondary or perhaps also a tertiary vertex and then summing the charge of the tracks associated with the decay chain. Preliminary results of such a study are illustrated in Figure 2, which shows the vertex charge reconstructed for charged and neutral B hadrons in 100 GeV b jets. For charged B hadrons, there is a strong correlation between vertex charge and the quark charge, whereas the case of neutral B hadrons will require further analysis, including the "charge dipole" approach pioneered by the SLD Collaboration, and will always be limited by the effects of  $B^0\overline{B}^0$  mixing.

Figure 2 Preliminary vertex charge distributions for 100 GeV b-jets.

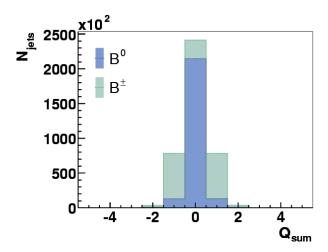

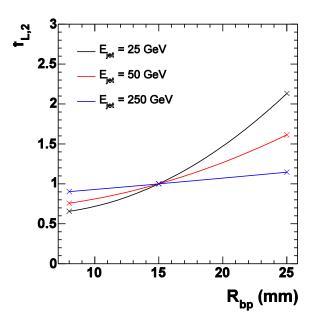

One measure of the efficacy of the quark charge selection is the leakage rate  $\lambda_0$ , i.e. the probability of reconstructing a neutral B hadron as charged. As quark charge selection requires the correct assignment of all tracks to secondary or tertiary vertices, this may be particularly sensitive to changes in the vertex detector design, such as increases in the radius of the beam pipe. Hence, LCFI has investigated the effect of such changes. The results of this study are shown in Figure 3. The leakage rate,  $\lambda_0$ , is seen to increase as the beam pipe radius  $R_{bp}$  is increased from 15 to 25 mm or if

the thickness of the vertex detector layers increases from  $0.1\%~X_0$  to  $0.4\%~X_0$  per layer. Increasing the minimum momentum of the tracks assigned to vertices from 0.1 to 0.2 GeV also leads to a notable degradation in performance. The results emphasise the need to push all these parameters to their limits, since in the real detector all these effects will add up.

Figure 3 Leakage rate as a function of polar angle for various detector designs and reconstruction procedures.

While the change in leakage rates discussed above may appear to be rather small, LCFI has shown that, for example, the detector with increased beam pipe radius would require an increase in integrated luminosity by about a factor of two in order to compensate for the loss in charge identification performance for physics processes relying on independent measurement of vertex charge in two jets, as is illustrated in Figure 4.

**Figure 4** Factor by which integrated luminosity has to vary to reach same physics sensitivity as the standard detector design for processes requiring vertex charge measurement for 2 jets, as a function of beampipe radius.

# The LCFI Vertex Package

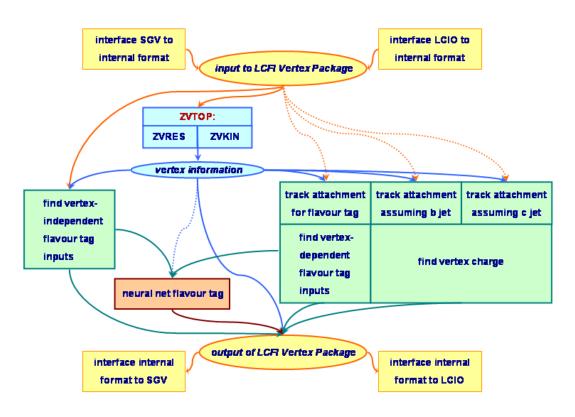

The LCFI Vertex Package is a comprehensive tool for using the information provided by the VXD for quark flavour and charge identification. Figure 5 shows a schematic overview of the Package, input to and output from which is handled in LCIO<sup>5</sup> format, permitting data to be exchanged between the different ILC software frameworks. For example, input can either be provided by the fast MC simulation SGV<sup>6</sup>, used by LCFI so far, thus allowing detailed comparisons and cross checks with previous results, or by MarlinReco<sup>7</sup>, the event reconstruction framework under development in Europe.

Figure 5 Structure of the LCFI Vertex Package and flow of information between the different parts of the software.

The vertex finder ZVTOP provides two vertexing algorithms, called ZVRES and ZVKIN, the latter is also known as the ghost track algorithm. While the ZVRES branch is a very general algorithm coping with arbitrary multi-prong decay topologies, ZVKIN is more specialised. Using additional kinematic information, the ghost track algorithm is able to correctly assign tracks to vertices in decay topologies with one or more 1-prong vertices, thus extending coverage and improving the flavour tagging capabilities as shown for SLD<sup>8</sup> where this code was first developed. Our package is the first to provide this algorithm for ILC studies.

The default flavour tag procedure provided was developed for the ILC by Richard Hawkings<sup>9</sup>. It is based on nine neural networks, three each for the three cases of one-, two- or more vertices found by ZVTOP. Separate networks are used to identify b-jets and c-jets for arbitrary background. For some physics processes the background only consists of b-jets, permitting improved c-jet identification. Therefore dedicated networks are provided for that case.

For training the neural networks and for obtaining the output from pre-trained neural nets we use C++ based neural network software developed within the LCFI group. This allows flexible definition of the network architecture (number of layers and nodes), transfer function and training algorithm.

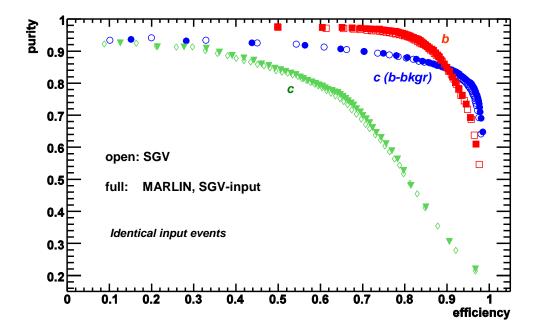

Studies of the LCFI package have so far been performed largely within the European ILC analysis framework MARLIN. The MARLIN package is based on a modular approach, permitting distributed code development. Agreement between the Vertex Package and earlier FORTRAN versions of the code is excellent, as is shown in Figure 6. Results agree equally well over the full ILC energy range.

**Figure 6** Comparison of purity of the flavour tags for b-jets, c-jets and c-jets with b-background only, plotted as function of efficiency, for a CMS energy of 92 GeV. Full symbols correspond to the result from our package in MARLIN, open symbols to the performance of previous SGV-FORTRAN code.

The LCFI code is available via the Zeuthen CVS repository for ILC software. In addition, another directory has been set up for descriptions of neural networks and information on the training conditions used for those networks, such as physics process, sample size, input variables etc. A central repository for these networks will contribute to making analyses based on these flavour tags more transparent and should facilitate comparisons between similar studies performed by different ILC groups.

# Future Programme

The optimisation of vertex detector parameters will continue until construction of the detector begins. This optimisation will be based on detailed performance comparisons both at the level of benchmark quantities and of physics processes sensitive to the vertex detector design. To yield reliable results, they must be based on realistic descriptions of the designs that are compared and be performed using adequate vertex detector simulation and reconstruction tools, requiring further development of the software in parallel to the optimisation process.

The benchmark quantities to be considered will include both direct measures of performance, such as impact parameter resolution, and measures of the overall performance of the flavour tagging and

vertex charge reconstruction. These will all be studied as a function of energy and polar angle. Various benchmark physics processes have been chosen in consultation with the ILC community. Clearly, as LHC results become available and new models are developed there will be changes in the physics processes for which the ILC machine and detectors should be optimised. LCFI will work closely with the global detector concept groups and our theoretical colleagues in this area.

The following subsections cover the improvements to the Vertex Package software currently envisaged, the benchmark physics processes that will be used for detector optimisation and the parameters and aspects of the vertex detector design to be improved as a result.

# Work related to the Vertex Package software

# **Near-term improvements of the code**

While the first version of the LCFI Vertex Package is already fully functional, providing a complete vertex finding package in ZVTOP, flexible flavour tag and vertex charge reconstruction and extensive documentation, near term improvements are envisaged to increase further the flexibility of the package and to permit the user to better monitor the effects of changing parameters in the Package. For this purpose, the possibility to write out diagnostic plots and tables with raw numbers will be added to all three parts of the package and the documentation further extended.

Calculation of the joint probability variable, one of the inputs of the default flavour tag algorithm, depends on parameters that have to be obtained from a fit to the track impact parameter distribution. In the first version, "hard-coded" approximate numbers obtained from fast Monte Carlo were used in this calculation. The next release will include a module to perform the fit required to ensure optimum parameter values are used.

Another known deficiency of the first version of the Vertex Package is that the vertex fitter implemented has not been optimised for run time performance and thus requires a large proportion of the execution time. This issue is currently being addressed by interfacing a fitter developed by the Darmstadt ALICE group to our code. The new diagnostic features will be used to ensure that vertexing results from the new fitter are compatible with those obtained from the first release version. These new features will be released to the community in autumn 2007.

The current Vertex Package uses MC information to suppress tracks resulting from photon conversions, hadronic interactions and from the decay of  $K^0_s$  mesons and  $\Lambda$  baryons. Development of masking algorithms based on information from reconstructed tracks is required and is underway. Adequate treatment of these effects will have to be in place, for example, for a realistic study of the effect of varying the material budget.

A further point that requires improvement is the treatment of the interaction point (IP). As no routine was available to determine the position of the IP, and in order to make our code available to the community as early as possible, a rather crude fit procedure was implemented. Throughout the Vertex Package, this should consistently be replaced by an IP based on averaging the event vertex over an adequate number of events. Development of code to do this has started.

Further work is also required on the default parameters of the package. While the current parameters partly stem from a combination of different previous studies with fast and GEANT3-based full MC, a systematic study is planned in which these parameters will be varied and new improved default values derived. Using these optimised parameters, new default neural networks for the flavour tag will be trained, which will replace the current networks that were trained using a fast MC sample.

To permit the Vertex Package to be used in conjunction with the ALCPG software framework, mainly developed and used in the US, compatibility with that framework will be ensured, e.g. through support for development of the appropriate "drivers", i.e. the java-modules corresponding to the processors already available in the MarlinReco framework.

# Improvements to flavour tag and vertex charge

It is expected that the flavour tagging algorithm and vertex charge reconstruction can be improved by using more of the information provided by the vertex detector and other subdetector systems than is currently the case, and by exploring new approaches to the tagging.

Both the flavour tag and vertex charge reconstruction will profit from the use of the ZVKIN vertexing algorithm for special decay topologies. The ZVKIN branch of ZVTOP, made available as part of the first release of the Vertex Package, has not yet been optimised for use at the ILC. In the ZVKIN implementation, the IP position is currently hard-coded and will have to be replaced by the fitted IP, as described above. The parameters of the ZVKIN branch were chosen on the basis of the SLD vertex detector performance, and may need to be changed to make full use of the improved ILC vertex detector design. Beginning with studies at the Z-resonance, where a comparison with SLD performance is possible, this parameter optimisation will subsequently be extended to higher energies. Once the ZVKIN branch is optimised, its use for improving the flavour tag and the vertex charge performance will be explored. Beginning with obvious areas where this algorithm could be helpful, e.g. for B hadrons with short decay lengths and single-prong decays, we will investigate how best to combine ZVKIN results with information from the ZVRES section of the vertex finder. For example, we will assess if a subset of cases can be identified in which ZVKIN results should replace those of ZVRES (e.g. in the flavour tag), or if results from both branches should both be used as inputs to the flavour tagging neural network (i.e. for the same jet).

Currently, the default flavour tag is based on the approach developed by R. Hawkings. Variations on this approach will be studied in order to see if it can be improved. Possible changes include a different choice of input variables and a different set-up of the neural nets that combine these inputs to obtain the tag. For example, currently different neural networks are used, depending on the number of vertices identified in the jet. We will investigate whether this provides optimal performance. The network architecture, i.e. the number of layers and the number of nodes as well as their transfer function, will be changed, and the performance of the different training algorithms provided by the Package investigated. Further, we have started to use new "data mining" approaches to the flavour classification problem, rather than neural networks. Initial studies suggest that methods such as decision trees may provide similar levels of performance.

Using information from other detector subsystems may allow further improvements in the tagging performance. For example, increasing the precision measurements of the effective mass of jets using high-energy neutral pions reconstructed in the fine-grained calorimeter may result in noticeable improvements in flavour tagging as this is one of the most powerful separation variables. Similarly, identification of leptons will help distinguish between b- and c-jets. Given that energy can be precisely measured for hadronic jets, while for semi-leptonic decays part of the energy is carried away by the neutrino, the ability to distinguish between jets containing semi-leptonic heavy hadron decays and purely hadronic jets would allow an improvement in the precision of the jet energy measurement. Another way in which one may profit from linking information from the different subsystems would be to use vertex-information to improve the assignment of tracks to jets.

So far, optimisation of vertex charge reconstruction for ILC conditions has been performed using a fast MC simulation. In the future, we will need study if the algorithm is still optimal when using GEANT4-based MC samples and realistic tracking as input. Determination of the quark charge sign is so far restricted to cases in which a non-zero vertex charge has been reconstructed. In b-jets containing a neutral hadron, the quark charge sign can in some cases be determined from the charge-dipole procedure, developed at SLD, which is based on the results of the ZVKIN branch of ZVTOP.

# Longer term plans

Tagging performance strongly depends on the errors of the input tracks. These track errors in turn depend on the hit errors from which the tracks are reconstructed. The hit locations and errors differ depending on the sensor technology assumed for the vertex detector. Currently, Gaussian smearing of the MC hit positions is used. The existing more sophisticated code is specific to the DEPFET sensor technology. For CPCCD and ISIS technologies, simulation code to adequately describe the processes in the sensors and the subsequent cluster finding step in the readout chip will have to be developed and used to address some of detector design issues that one can expect to show a significant dependence on these effects.

An example is the performance in the forward region, which is particularly relevant for the physics processes of interest at the ILC. This is related to the question of whether better performance is achieved with a long barrel vertex detector or with a design with a short barrel plus end-caps.

Software to simulate the alignment procedure for the detector will be needed to study the effects of misalignment and tolerances for the positions of sensors along the beam and perpendicular to it, determining the amount of sensor overlap required and hence influencing the detector design. Such software thus either has to be developed or existing software adapted and/or interfaced to the ILC software framework to perform these studies.

## Studies of benchmark physics processes

While performance studies of impact parameter resolution, flavour tag and vertex charge reconstruction can already provide a wealth of information on which detector designs are preferable, a realistic investigation of the trade-offs between different designs will require comparing them at the level of the resulting measurement precisions achieved for relevant benchmark processes. Care needs to be taken in the choice of these processes, since they have to be

both typical of the physics that the ILC will give access to and be sensitive to the vertex detector design. Theorists and experimentalists from the ILC community have studied which processes would best be suited for this purpose, and a report on recommended processes, chosen by a dedicated "physics benchmark panel" was published some time ago. This forms the baseline for the selection of the processes that will be studied during the preparation of the LoIs and the engineering designs.

Processes sensitive to the vertex detector design cover the areas of Higgs physics, SUSY studies and indirect searches for new physics. The remainder of this subsection describes which studies are currently underway, with further ones likely to be added in future.

Measurement of the Higgs branching ratios, especially for the decays of a light Higgs boson into  $b\bar{b}$  and  $c\bar{c}$ , will be demanding in terms of vertex detector performance. While the recent study by Kuhl and Desch<sup>10</sup> was based on a fast MC simulation, with a parameterization of vertex detector performance derived from GEANT3-based full MC, new GEANT4-based studies are now under way in the LCFI group, aiming at a realistic comparison of different detector designs.

A study of  $e^+e^- \rightarrow ZHH$ , performed in coordination with the SiD benchmarking group is also beginning. Analysis of the resulting multi-jet final states, with a large number of b-jets, will require excellent flavour tagging performance, and could profit from quark charge sign selection and the possibility to improve track-to-jet assignment using vertexing information.

As shown by Hewett and Riemann<sup>11</sup>, the process  $e^+e^- \rightarrow b\bar{b}$  will provide excellent sensitivity to new physics at the ILC. An LCFI study of this process has now begun and will, for the first time, take into account the experimental limitations that arise from realistic flavour tagging, as well as from quark charge sign selection.

Another indirect search for new physics being performed by LCFI is the study of anomalous Wtb coupling in  $e^+e^- \rightarrow t\bar{t}$ . Key observables for this study, such as forward-backward asymmetries and spin correlations, strongly depend on vertex detector information and hence permit the detector design to be optimised.

Cosmological data, such as the recent WMAP results, strongly constrain the SUSY parameter space. Some minimal supersymmetric models could favour a light sbottom decaying to give rise to a low-momentum b-jet in the final state. Detection of these jets with sufficient precision will be sensitive to the amount of material in the vertex detector. Guided by theoretical studies of which SUSY parameters correspond to a small sbottom neutralino-mass splitting, performed at RAL/Southampton, LCFI will use a GEANT4-based detector description to study detector effects, and determine the ILC-sensitivity to the process using realistic tracking and vertexing.

#### Optimisation of the Vertex Detector design

Different vertex detector designs will be simulated in GEANT4 and compared both at the level of the performance of flavour tag and vertex charge reconstruction and at the level of the resulting measurement precision obtained in physics benchmark processes such as those described in the previous subsection.

Different geometrical arrangements of the sensors will be compared and the results related to questions regarding support materials and required sensor overlap and linked to alignment studies. GEANT permits different support structure materials to be simulated, including foams such as those composed from silicon carbide and reticulated vitreous carbon. The type and amount of material present in support structures, sensors and readout and drive electronics will be varied and the resulting performance compared and fed back into the ongoing design work in the mechanics work package (WP6).

It should be noted that not only the amount of material in terms of interaction and radiation lengths is relevant, but also the fraction of the total volume taken up by sensors and support. This is because the suppression of hadronic interactions may require discarding vertices found in the volume occupied by material. If this is a large fraction of the total vertex detector volume, inevitably decay vertices important for the reconstruction of physics processes will also be discarded as MC simulations having shown that, for  $e^+e^- \rightarrow b\bar{b}$  events at a centre-of-mass energy of 500 GeV, over 40% of tertiary vertices and roughly 25% of secondary vertices are located beyond the first vertex detector layer.

A study of the effect of varying the beam-pipe radius will be performed which, in contrast to the earlier LCFI study presented at Snowmass<sup>12</sup>, will be based on full MC, take into account the effects of  $e^+e^-$  pair background and include the evaluation of flavour tag, vertex charge and resulting physics benchmark performance.

# Estimate of required effort

The effort required to realise the above programme, including developments for both the ILD and SiD detector concepts where appropriate, is estimated to be:

- Near term improvements of the code: 2 person years.

- Improvements to vertex tag and vertex charge: 8 person years.

- Studies of benchmark physics processes: 25 person years.

- Vertex detector optimisation: 6 person years.

Many of the above research topics will make excellent PhD and Diploma theses and LCFI would hope to continue to effectively employ students to help perform these studies.

# WP2 - Sensor Design and Production

## Introduction

This Work Package is responsible for the design and production of the two sensor types that LCFI is developing for the VXD of the ILC, the Column Parallel CCD and the In-situ Storage Image Sensor. Two generations of CPCCD have now been manufactured by e2v technologies. With the first of these, CPC1, LCFI was able to demonstrate that the parallel readout concept it developed with e2v can be successfully realised. CPC1 is a two-phase device, with pixels of size  $20 \times 20 \ \mu m^2$ . Testing thus required the bump-bonding of a Column Parallel Readout chip to the CPC1 on a  $20 \ \mu m$  pitch which was carried out by VTT and represents the first time bump-bonding has been performed with an e2v CCD.

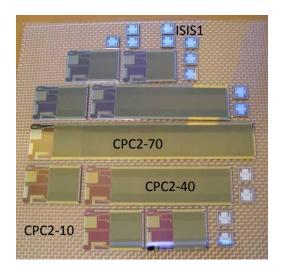

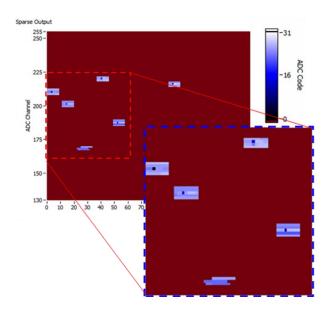

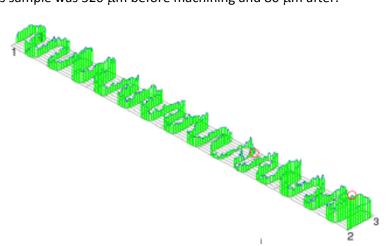

The second generation of CPCCDs, the CPC2, includes devices close to the size required for the VXD, as is shown in Figure 7. In particular for the largest version of these CCDs, the distribution of the high speed clock pulses becomes problematic. The resistance of the buslines and the polysilicon gates to which they supply the clock signals is sufficient to significantly degrade the clock amplitude at the points most remote from the drive signal input. Metal buttressing of the polysilicon gates goes some way to solving this problem, but the large intergate capacitance of the CCDs and the large clock currents that are needed as a consequence thereof ensure that this is not enough. Some of the CPC2 devices therefore incorporate a further innovation developed by LCFI, a double metal layer which allows the entire CCD surface to be used for distribution of the clock signals. The first metal layer is separated from the gates by a layer of silicon dioxide, through which connections are made to the phase one gates. The second metal layer is insulated from the first using a layer of polyimide. Connections are made from it to the phase two gates through holes in the lower metal layer. Similar holes are introduced into the upper metal layer to ensure that the clock distribution is as symmetric as possible. The testing of these "busline free" CPC2 devices is described in the WP5 section of this report.

Figure 7 The sensors resulting from dicing one CPC2 wafer; the size of the imaging area of the CPC2 sensors varies from  $13 \times 15 \text{ mm}^2$  (CPC2-10) to  $92 \times 15 \text{ mm}^2$  (CPC2-70). Several In-situ Storage Image Sensor (ISIS1) chips were also incorporated on this wafer.

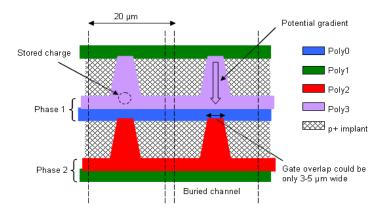

While the double-level metal concept provides a route to clock distribution in the CPCCD, reducing the capacitance of the device and hence the currents needed to drive it remains desirable. This would simplify the drive circuitry and also reduce the power consumption of the device. LCFI has therefore designed a range of novel structures aimed at reducing the main component of the CPCCD capacitance, that between the gates. These CPC-T devices, currently being manufactured by e2v, include structures such as that illustrated in Figure 8. In this "open phase" concept, the geometrical overlap between the gates is reduced, leading to decreased capacitance. More than twenty variants of the CPC-T will soon be available for testing and promise to provide reductions in the intergate capacitance as large as a factor of 4. The most successful of these new concepts will be incorporated in subsequent designs of the CPCCD.

**Figure 8** An "open phase" CCD structure, one of the approaches to reducing the intergate capacitance of CPCCDs being explored by LCFI.

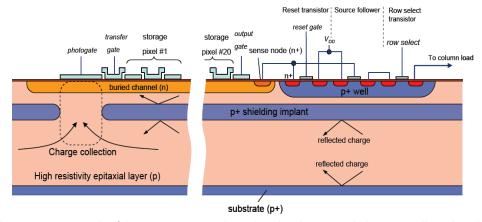

Progress with the design of the second sensor that LCFI is developing, the ISIS, is as yet less advanced. This new sensor is ideally matched to the ILC environment. The concept, illustrated in Figure 9, allows storage of the signals in small CCD-registers incorporated in each pixel during the bunch train. This is extremely robust, making the signal charge of 2000 e<sup>-</sup> or so immune to any electromagnetic interference (EMI) that is present at the ILC. Conversion of the stored charge and readout occurs during the intertrain gap, when the major source of EMI has been removed and allowing relaxed column parallel readout speeds of about 1 MHz.

**Figure 9** The operating principle of the ISIS sensor, signals produced in the epitaxial silicon are collected on the photogate and transferred to an in-pixel CCD register 20 times during the ILC bunch train. The CCD and on-pixel electronics are protected from the signal charge by the deep p+ shielding implant.

Proof of principle devices, with and without the p-well illustrated in Figure 9, have been successfully tested by LCFI. All control signals were generated externally in these large pixel proof-of-principle devices and efforts in this WP are now concentrating on designing devices with pixel sizes closer to those ultimately needed and in which the control signals can be produced on chip. This requires the production of very small CCD registers and the marrying of CMOS and CCD processes in the fabrication procedure.

Small pixel CCDs are already routinely produced by several manufacturers. Typically, however, these devices do not have the overlapping polysilicon gates found on the larger pixel devices manufactured by e2v. This can lead to problems when they are irradiated. Electron-hole pairs are produced in the  $Si O_2$  insulation between the gates and while the electrons rapidly diffuse away, the holes remain trapped in the  $Si O_2$ . With overlapping gates, where the gate polysilicon extends over the intergate  $Si O_2$ , this does not cause large potential shifts in the silicon between the gates. If, however, the gates do not extend over the intergate  $Si O_2$ , the trapped positive charge may significantly affect the potential in the underlying silicon. The signal electrons may then be prevented from travelling through the silicon by the potential pocket caused by the trapped charge and hence never reach the readout electronics.

A further requirement is that the small CCD registers can be driven with voltages compatible with CMOS electronics. CCDs are typically operated at relatively high gate voltages and reducing these may lead to increases in the Charge Transfer Inefficiency (CTI).

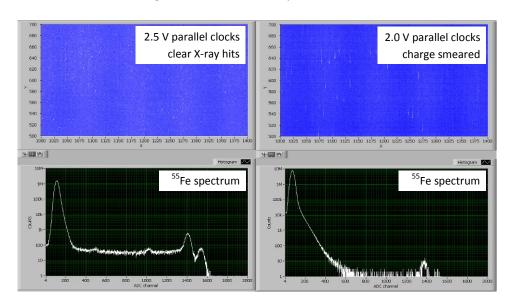

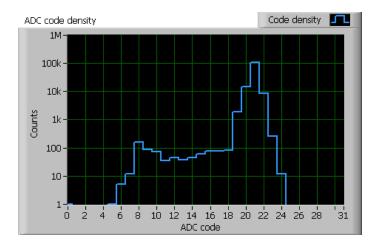

Figure 10 Performance of DALSA FTF2416 at very low parallel clock amplitudes. Even at 2.1 V, the Mn  $K_{\alpha}$  and  $K_{\beta}$  lines are clearly resolved due to the very low readout noise. The serial clock frequency is 20 MHz. This level of performance was maintained after irradiation.

LCFI has studied these problems using several FTF2416 CCDs which were provided by DALSA. These are 4 Mpixel image sensors with 9  $\mu$ m square pixels and non-overlapping gates, a technology which could produce 3-phase pixels as small as 2.5  $\mu$ m. The FTF2416 CCDs were tested, irradiated and tested again. As is shown in Figure 10, these behaved very well. Drive voltages as low as 2.1 V resulted in excellent performance, which was maintained after irradiation with a  $^{90}$ Sr source to doses of 76 krad. This gives us confidence that the CCD registers of the ISIS can be constructed using

existing non-overlapping gate fabrication procedures and design studies are now proceeding on this basis with several manufacturers.

# Future Programme

# **Column Parallel CCD developments**

LCFI will continue the CPCCD development by designing and manufacturing a third generation device in the second half of 2009. The CPC3 chip will be a fully custom, large CCD, manufactured on 6" wafers. The chips will have sizes of approximately  $120 \times 20 \text{ mm}^2$ , large enough for construction of prototype ladders. The CCDs will be back-thinned to  $20...50 \, \mu m$  as part of the integration process with the readout and driver chips. Due to the large device size, only 2...3 CCDs can fit on a wafer and the yield is expected to be below 10%, necessitating the production of the order of a few hundred wafers. The total design and manufacturing cost is estimated to be at least \$1000k.

The design of CPC3 will be influenced heavily by our two previous successful prototypes, CPC1 and CPC2. The results from our dedicated CCD test series for capacitance and clock amplitude reduction (CPC-T) will also be taken into account after evaluation in early 2008. The main goal of the CPC-T device tests is to verify that the effective CCD gate capacitance can be reduced by at least a factor of 2, which would greatly simplify the on-chip clock distribution. If no significant capacitance reduction can be achieved, then the "busline-free" 2-level metallisation from CPC2 is likely to be refined and used in CPC3.

The CPC3 mask set will also contain a smaller CCD with common design (CPC3-S) for tests of the readout and driver chips and some aspects of the integration without using the valuable large area CPC3.

One still unresolved issue is the type of CCD outputs to be used in CPC3. In CPC1 and CPC2 there are two types, voltage output via a single stage source follower and direct charge outputs. Single stage source followers require about 2 W of continuous power on the CCD, while the charge outputs consume no power. The voltage channels have been much better evaluated than the charge channels in CPR1 and CPR2. The CCD outputs are connected to the relevant voltage or charge CMOS amplifiers on the readout chips, which use similar power. Assuming 120 CCDs and a 1% duty cycle, the additional power dissipation from the single stage source follower outputs for the whole detector is 2.4W. Given this small difference in power, the final choice will depend upon the performance of the two types of readout chains. This is being evaluated in the present CPC2/CPR2 assemblies and will be studied further in the forthcoming CPC2/CPR2A configuration.

Due to the nature of the remaining R&D work, there is some uncertainty in the output of the CPCCD programme, in particular in the transfer of results from CPC-T to CPC3. This could delay the design of CPC3 or necessitate construction of another small-scale test device before the full size CCD is made.

## **ISIS** developments

The ISIS programme is presently less mature than the CPCCD development, but the potential benefits of a successful ISIS device on the performance of the vertex detector make it worth pursuing.

LCFI plans to design and manufacture a second generation ISIS2 chip in the first half of 2008. ISIS2 will be a small device, of size about 1 cm<sup>2</sup>, and will incorporate an array of pixels with all the necessary on-chip logic for addressing and clocking. No dedicated readout chip is envisaged for the ISIS2, instead a sufficiently wide contiguous block of columns (e.g. 16...32) will be read out by discrete external electronics.

With the ISIS2, LCFI will aim to demonstrate the functionality of a device with 20 CCD storage cells in a pixel that is not much larger than the target of  $20 \times 20 \,\mu\text{m}^2$ . The most important goals for ISIS2 are:

- Demonstrate CCD buried channel operation in a submicron CMOS process.

- Successfully use a p+ implant to shield the CCD storage register from parasitic charge collection. This implant should not interfere with the buried channel doping.

- Integrate control and clock driving in CMOS logic on the chip.

The ISIS2 will probably be made on a 0.18  $\mu m$  CMOS process. The CCD gates will be non-overlapping, unlike those of a traditional CCD, because 2-level polysilicon is not offered as part of the CMOS process. Our radiation damage tests of a CCD made with non-overlapping gate technology did not show any problems from the open gaps between the gates, and we are reasonably confident that there is no additional risk in using this design.

In ISIS2 we will integrate  $256 \times 256$  or  $512 \times 512$  pixels in the largest device, as well as several smaller arrays designed to test different variants of the architecture.

We are planning to manufacture the next generation ISIS3 in the second half of 2009. The ISIS3 will be a full-scale chip with similar dimensions to the CPC3. To achieve this, the ISIS3 will have to use stitching, which is routinely done in CCD processes but is a relatively novel area for CMOS manufacturers. In addition to the standard costs for the masks and wafer production, we expect to contribute towards setup costs and development for the stitching. The yield of such large area CMOS chips is unknown and if it turns out to be very low this could be a showstopper. We are planning to start work with the chosen vendor during the ISIS2 design and manufacturing phase to establish the potential risks as regards yield and develop methods to circumvent these where possible.

An additional advantage of using the CMOS process for the ISIS is the possibility this offers of integrating the readout electronics in a single monolithic device. Because the ISIS is read out in a column parallel fashion, as is the CPCCD, the front-end voltage channels and ADCs from the CPR development line are directly applicable to the ISIS. All the information from the ISIS can be transferred off-detector in the 199 ms available for readout in the intertrain gap without the need to for data sparsification. The transfer of the front-end architecture from the CPR chips into the CMOS process for ISIS3 may require some re-design because of the different feature size (0.25  $\mu$ m in CPR1/2, 0.13  $\mu$ m in CPR3).

We will also produce a smaller device (ISIS3-S) with the same design as ISIS3 but with a reduced number of rows. The yield of ISIS3-S is expected to be higher than that of the more expensive full

size ISIS3 and the device will be used for most of the tests. The design and production costs for the ISIS3 are expected to be around \$1000k.

## **WP3 Readout and Drive Electronics**

## Introduction

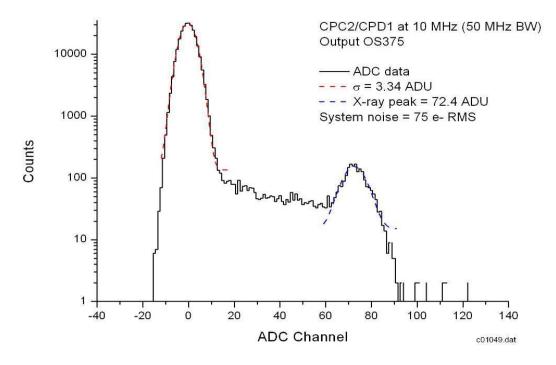

This WP is concerned primarily with the design and production of the drive and readout ASICs for the Column Parallel CCDs which LCFI is developing. The device that has been designed to produce the clock signals is the Column Parallel Drive chip, CPD1. This chip is described here, and information on its testing is given in the WP5 section of the report. Readout for the CPCCDs is provided by the Column Parallel Readout chips CPR1 and CPR2, the pitch of which must match the  $20 \times 20 \ \mu m^2$  size of the pixels of the CPCCDs. The CPR1 and the CPR2 are described briefly here, as is the design of the CPR2A, which addresses some of the problems identified in the testing of the earlier readout chips.

## CPD1

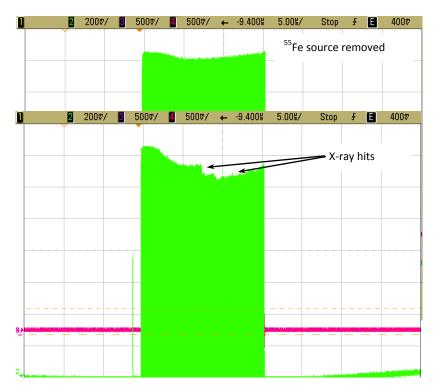

This CPCCD clock driver ASIC is optimised to produce the high currents of up to about 20 A that are necessary to drive the CPCCDs. The CPD1, shown in Figure 11, provides signals to drive the two-phase CCD gates at 50 MHz and 25 MHz in the inner and outer layers of the VXD, respectively. The capacitance of the sensors is about 40 nF in the inner and 130 nF in the outer layer. Higher currents are thus needed to drive the larger outer layer sensors, despite the lower frequency at which these are operated.

Figure 11 Photograph of a CPD1.

The CPD1 has a size of 8 × 3 mm², with the main power supply pads, on a 100 micron pitch, along one of the long edges of the chip and the clock outputs on the other. The control pads are placed along one of the short edges, on a 200 micron pitch. The CPD1 layout is segmented into 8 blocks, each with 4 pads for phase 1 and 4 for phase 2. The segments are enabled when the corresponding bits in the control register are set high. This allows the CPD1 to be used with a wide range of load capacitors. Testing this chip is complicated by the effects of the inductance of any wire bonds used to connect it to an external load. Hence, for test purposes, two driver outputs are permanently connected to an on-chip 2 nF capacitor via wide metal tracks. The driver performance for these channels is not limited by the external bond-wire inductance and is closer to that achievable when the CPD1 is bump-bonded to a sensor. The configuration of the drive pads on the CPC1 and CPC2 does not allow this, so tests with a bump-bonded CPD1 must await further generations of the CPCCD.

The chips have programmable current limits, so triangular-wave drive is possible over a range of frequencies down to about 100 kHz. The triangular signal shape results in lower currents than for square waves, which minimises clock feed-through and power supply transients. Positive and negative currents are independently adjustable, which allows balancing of the two clock phases.

#### CPR1

The CPR1 is an ASIC that can readout 250 columns of the CPC1 and CPC2 sensors. Half of the CCD columns are connected to voltage amplifiers which are driven by the source followers on the CCD. The other columns, which do not have source followers, are connected directly to charge amplifiers on the readout chip which have 3 fF feedback capacitors. Both types of amplifier are designed to produce signals of about 100 mV for the signal of 2000 electrons that is typically produced when a minimum ionising particle traverses the 20  $\mu$ m thick epitaxial layer of the CCD.

The signals are digitised by 5-bit flash converters laid out on the same pitch as the CCD (20 microns) and the results are stored in a memory array, accessed via read and write pointers.

The CPR1 has been bump-bonded to the CPC1 and tested with X-rays. Both the voltage and the charge channels worked well, but there were some variations between channels and limitations in the operating range of the ADC.

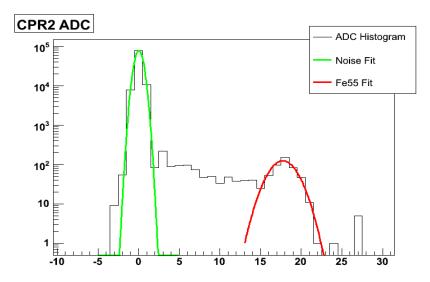

#### CPR2

The CPR2 is a considerably more ambitious development of the CPR1. The same layout is maintained, with charge and voltage sections on a pitch allowing the chip to be bump-bonded to the CPC1 and CPC2 and the chip is fabricated using the same IBM 0.25  $\mu$ m CMOS process. Improvements to the analogue circuitry are made and data sparsification logic is added to the chip. The distribution of the ADC clock signals is also improved, allowing faster clock edges across the whole chip width. This overcomes the ADC range problems observed in CPD1 and gives better uniformity.

The sparsification logic detects cluster kernels of  $2 \times 2$  pixels in which the signal is above a global threshold. An extended cluster of size  $4 \times 9$  is then defined around this kernel and read out. Timestamp and positional information are attached to the charge data from the pixels.

As is described in the WP5 section of this report, the voltage amplifier sections of the bump-bonded CPR2/CPC2 assembly work well over a wide range of ADC settings. The charge amplifiers, however, suffer from some noise or instability, perhaps due to fluctuations in the substrate voltage. It is possible that this is caused by the increased amount of clock buffering in the ADC, with its associated power supply transients. Such interactions illustrate the necessity to plan for several development cycles in a project as complex as the design of the readout chip for the VXD sensors. It is extremely difficult to anticipate or simulate all aspects of the behaviour of such a chip. As is discussed below, LCFI anticipates that at least two further CPR generations will be needed before it has a chip able to readout full size sensors at the data rates imposed by the ILC.

Tests of the CPR2 have also shown that, while the analogue offset matching is improved compared to the CPR1, there is still some gain variation in the voltage amplifiers. The sparsification logic functions well, but dead-time is introduced at high occupancies due to the limited memory available on the CPR2.

#### CPR2A

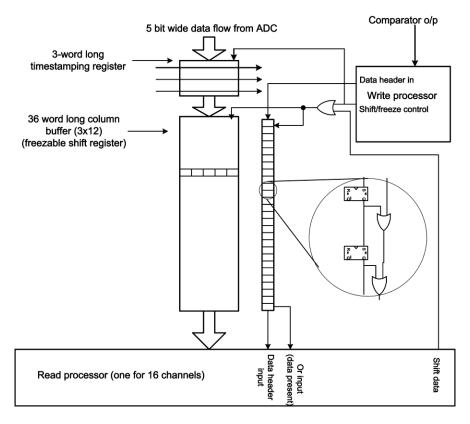

The CPR2A is an iteration of CPR2. The same layout is maintained, allowing it to be used with the available CPC2 sensors. Major improvements have been made in the data handling. Compaction of the CPR2 layouts has allowed an increase in memory depth by a factor of three, as is illustrated in Figure 12. The CPR2A can process more complex sequences of clusters, including those close together in time. This makes a big difference in the ability to handle realistic patterns of data derived from physics simulations. The ADC clocking will operate with lower drive capacity: it has been tuned to allow propagation of the signals across the chip while reducing the power supply transients. This is expected to stabilise the charge amplifiers, allowing a realistic comparison between voltage and charge readout modes.

**Figure 12** A block diagram of a section of the CPR2A showing the extended column buffer which can store 36 words of data, enough for 3 clusters including the time-stamp data. A data header register has been added in order to keep track of multiple clusters within the column.

# **Future Programme**

The steps foreseen in the development of the readout and drive chips for the LCFI sensors, culminating in the production of chips that are suitable for use in the VXD, are described in the following.

# CPR2A design and testing

The design of the CPR2A is largely complete, but some details still require implementation. One of these is the addition of a calibration test register. This will allow the injection of test signals directly to selected analogue inputs, a useful facility for the testing of the chip. Before submission for fabrication, simulations of the charge and voltage amplifiers will be performed, including a full

description of parasitic effects, in order to understand the gain variations seen in CPR2. Some further optimisation of the layout of the amplifiers and ADCs will be performed in order to improve analogue performance.

Once the CPR2A has been manufactured, a full evaluation of its digital functionality will be performed. Thorough tests of the charge- and voltage-mode amplifiers and the ADC will also be carried out using for wire-bonded CPR2A chips. These tests will cover a wide frequency range, and will use the on-chip calibration register where appropriate.

Tests of bump-bonded assemblies of the CPR2A and the CPC2 will then be carried out, with particular emphasis on understanding and optimising the amplifier performance. One of the aims of these tests will be to decide whether to use the charge or voltage mode for future designs.

#### CPR3

The next generation readout chip, the CPR3, will have a width of about 11 mm and be designed to readout a CPCCD with 500 channels. The CPR2A design with the preferred amplifier configuration will be translated to the CPR3 dimensions on a 0.13 micron CMOS process. The chip will be modified to simplify the drive signals and analogue biasing, reducing the number of pads needed for control signals and the complexity of the test board. The digital circuitry will be optimised for the wider CCD format and more complex data handling algorithms will be implemented to minimise dead-time effects at higher occupancies. In particular, options for high-speed data transfer off the CPR3 will be explored. This will include investigation of non-sparsified read-out, which becomes favourable if background rates increase significantly over current predictions.

After final design, layout and manufacture, the performance of the CPR3 will be verified in wire-bonded format before full testing of the CPR3 bump-bonded to the CPC3.

## CPR4

Currently we foresee that the CPR4 will be the chip used in the VXD. It will have a width of 21 mm, matching that of the full scale CPCCDs, and will be capable of reading out about 1000 channels. The CPR4 will be an adaptation and development of the CPR3 design, taking into account the results obtained in the testing of the CPR3. Particular care will be needed in the modelling of parasitic capacitances and resistances in order to maintain the high speed capability of the chip over its extended width.

Again, following final design, layout and manufacture, the performance of the CPR4 will be verified in wire-bonded format before full testing of bump-bonded CPR4/CPC3 assemblies is carried out.

# Design challenges for CPR3 and CPR4

The particular challenges we anticipate in the design of the CPR3 and CPR4 include the transmission of digital signals over the extended chip width without creating too much digital noise on the power supplies and the substrate. The switch to 0.13 micron technology will help here, as the additional metal layers have much reduced capacitance to substrate. Metal layers can also be connected in parallel to produce lower resistance.

A further challenge is that of getting the large amounts of data off the chip generated even at only 1% occupancy. This implies that a large number of digital output pads must be driven at high speed in order to cope with the data rate. It may be possible to adopt low-voltage and/or differential signalling to minimise the resulting coupling to the sensitive analogue inputs. Such coupling could easily cause unacceptable noise levels.

Translation of the CPR2A design to a smaller CMOS process will be non-trivial in some areas. The analogue designs may need to be reconfigured to work at the lower supply voltage. The 0.13 micron process has the option of dual power supplies, of 1.2 V and 2.5 V, which could be a solution for some blocks of circuitry.

# **Budget and time scales**

Wafer costs for the above development are likely to be in the range of \$800 k to \$1000 k.

The time anticipated for the completion of the CPR2A is 2 months, with one engineer working full-time on the project. It is anticipated that the manufacture of the CPR2A will take 3 months and that testing of the CPR2A in wire-bonded mode will take an additional 2 months.

It is expected that the design of the CPR3 will take about 12 months. We plan to start this work immediately after the submission of the CPR2A chip. CPR3 manufacture is likely to take 3 months, but would not be started until successful testing of bump-bonded CPR2A/CPC2 assemblies. As in the case of CPR2A, we anticipate that testing the CPR3 in wire-bonded mode will take 2 months.

Following successful CPR3 testing, a design period of 6 months is assumed for CPR4 design with subsequent periods of 3 months for manufacture and 2 months for testing in wire-bonded mode. We thus consider it possible to begin tests of a bump-bonded CPC3/CPR4 assembly in 2010.

## **WP4 - External Electronics**

#### Introduction

The testing of the sensors described in this report requires the development of electronic systems which provide all the necessary control, biasing and monitoring functions needed for the sensors. This is the responsibility of Work Package 4, as is the provision of the interface for the CPCCD and its column parallel readout (CPR) chips to the external world, the test systems for the column parallel drive (CPD) chips, boards for the study of the CPC-T devices and test systems for the ISIS devices. All these require careful design, for example in the case of the CPCCD test systems because drive signals with significant current have to be supplied at high frequency without causing noise which could disturb the small signals from the sensors. Significant electronic engineering expertise is therefore needed for the success of this Work Package.

In the following, examples are given of some of the developments that have recently been made, such as the test boards for the CPD1 and CPC-T, the latest motherboard for the testing of the CPC2 and the transformer drive that was developed for test purposes before future developments are discussed.

## **CPD1** test board

An example of the boards that have been constructed for the testing of individual components is that produced for the CPD1 driver chip. This was designed to allow the full functionality of the chip to be exercised and allows the connection of a capacitive load with low inductance. The board is controlled by the Collaboration's BVM2 VME module, which downloads control information to a shift register in the CPD1 through a serial link and also provides all the necessary timing signals. One such board is shown in Figure 13.

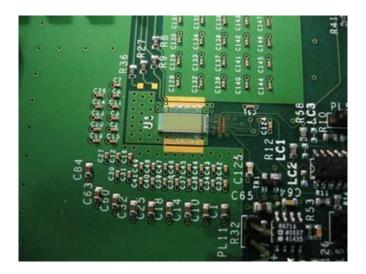

Figure 13 A CPD1 chip mounted on its test board.

## **CPC-T test board**

A further board has been produced for studying the CPC-T test devices. The board has three main functions: to clock the CPC-T at frequencies of up to 50 MHz, to amplify four output signals and to

measure the gate capacitance. The capacitance is measured by observing the clock current in the clock line. This is done using a differential amplifier connected across a small series resistor.

#### **CPCCD** motherboards

The development of the motherboards for the testing of the hybrid CPCCD/CPR assemblies is a challenging task due to the large number of components and the overall complexity of the systems. The boards must provide all the bias voltages for the CPCCD, the necessary drive signals and cater for the electronics associated with the readout chips. In the motherboard, the assemblies are placed in a well in the PCB to minimize the length of the wire bonds connecting the CPCCD to the clock driver system. The boards are equipped with low noise amplifiers for the discrete source follower outputs on the CPCCD which allow access to the analogue output signals. They also feature temperature monitoring and control for work in a cryogenic environment.

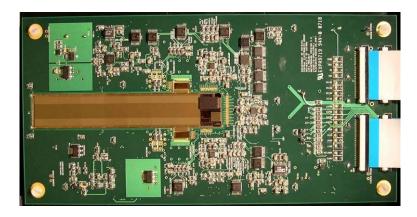

The focus of recent work on motherboard design was the production of motherboard 5.0 (MB5.0) which uses the CPD1 driver chip. The part of the board responsible for the driver chip is a new addition to the motherboard designs. MB5.0 also uses an improved grounding scheme and four 50-pin onboard Flexible Flat Cable connectors provide a tidier solution for connections to and from the boards than the previous cabling arrangements. A photograph of a fully assembled MB5.0, with a CPC2-70 and two CPD1 chips attached, is shown in Figure 14. The first MB5.0 has been successfully used for the busline free CPC2 testing described in the WP5 section of this report.

Figure 14 A CPC2-70 sensor mounted in a MB5.0 with one CPR2 readout and two CPD1 driver chips.

Earlier versions of the motherboard, assembled before the CPD1 ASIC was available, used either commercial driver MAX5057 chips or transformers constructed in the multilayer PCB and driven by a RF amplifier to provide the drive signals for the CPCCDs.

#### Transformer drive

Miniature air-cored planar transformers, implemented in a multi-layer PCB, offer a relatively inexpensive and easy to implement solution for the drive system of the CPCCD. The gate impedance of the CPCCD at high frequencies is very low and is dominated by the capacitance. Step-down transformers can provide the high current needed to drive this large capacitance, in excess of 10 A even for the smaller CPCCDs. A transformer ratio of about 16:1 allows the primary winding to be driven from a commercial RF power amplifier.

Measurements of the double level metal CPC2 sensors performed using such a system successfully demonstrated operation at 45 MHz, but showed the limitations of our first implementation of the transformer drive. The tests revealed a phase imbalance at high clock frequency. Simulations showed that parasitic inter-winding capacitance in the transformer is responsible for this effect. An optimized transformer design with circular coils is now under investigation. This will be implemented in the next revision of the motherboard with transformer drive. Now that it is clear that the CPC2 can be driven at frequencies of 45 MHz, as described in the WP5 section, this system can be optimised for a narrower range of frequencies.

## **Data acquisition**