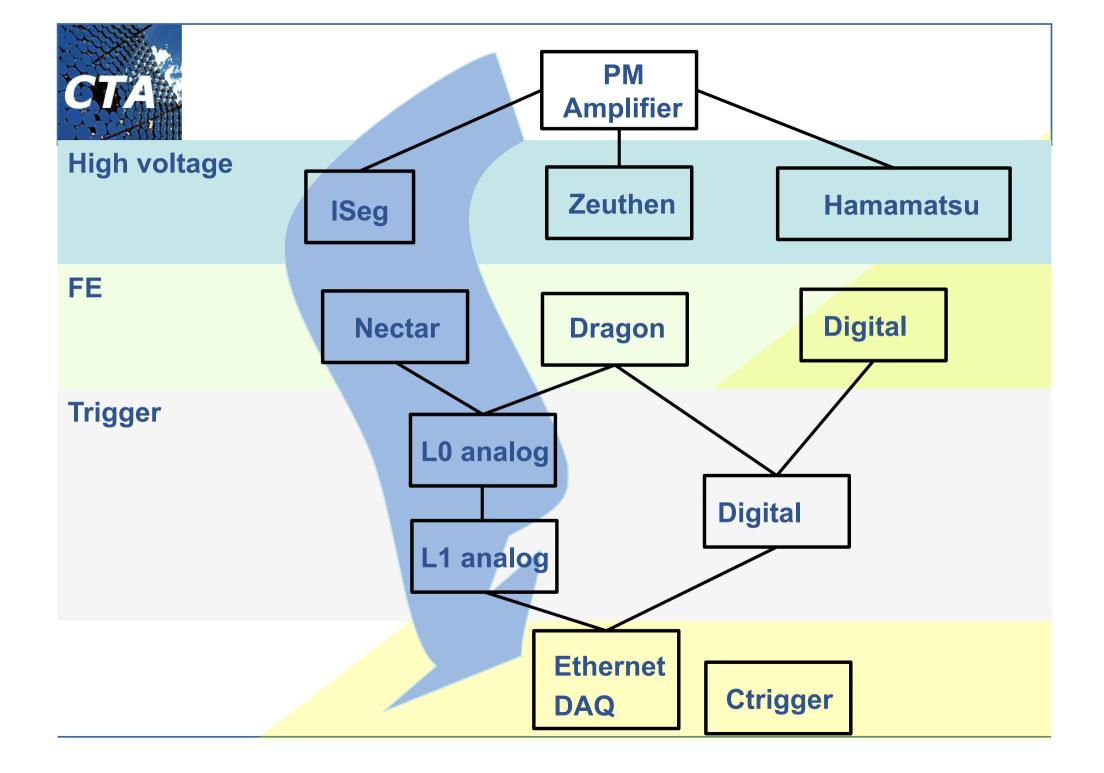

## New Electronics for the Cherenkov Telescope Array

- Idea: use a front end board similar to those of HESS/HESSII

- FEB layout based on the use of analogue memories (ARSO for HESS, SAM for HESS2)

- Analog trigger with comparators

- Collaborative efforts with french and spanish labs

- Special attention paid to price/power consumption reduction

JF. Glicenstein (for the NECTAr team)

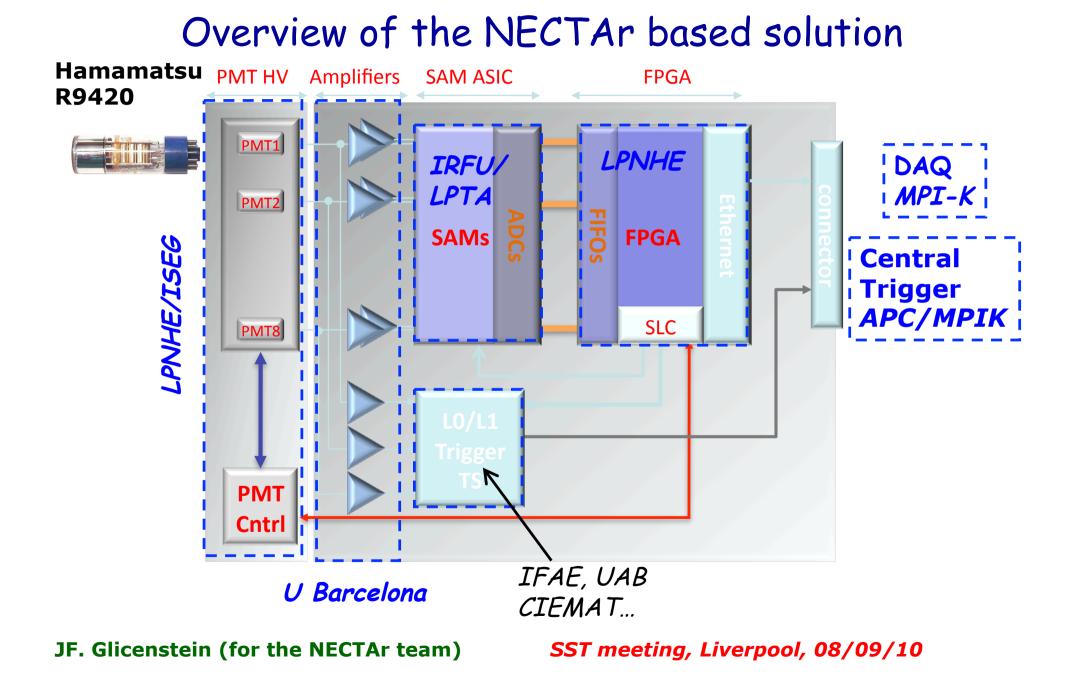

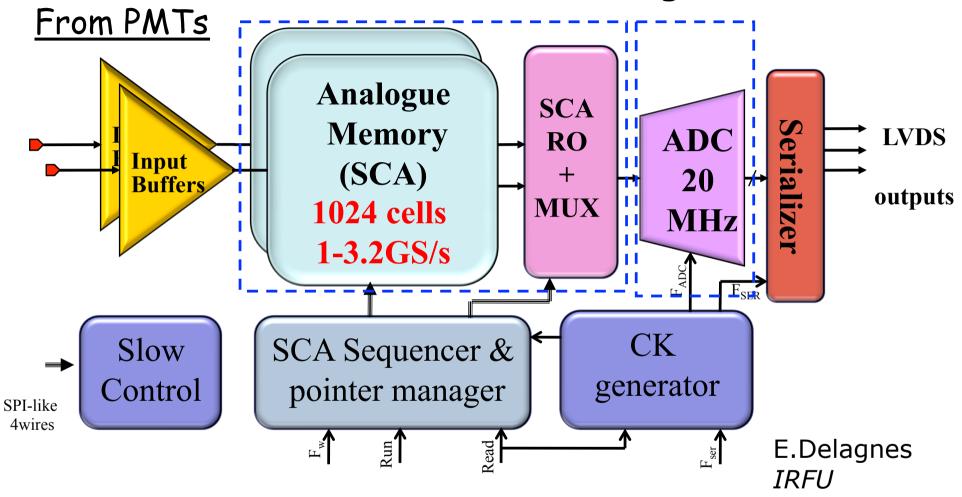

### NECTARO block diagram

- Fast analog sampler/memory + digitizer.

- 2 differential channels (1024 cell memory each)

JF. Glicenstein (for the NECTAr team)

#### NECTAR requirements: almost identical to those of SAM.

| NAME                                             | SAM                                    | Nectar0<br>(expected) | Unit    |

|--------------------------------------------------|----------------------------------------|-----------------------|---------|

| Power Consumption                                | 300                                    | 150-300               | mW      |

| Sampling Freq. Range                             | <1to 2.5<br>(3.2)                      | 1 to 3.2G5/s          | GS/s    |

| Analog Bandwidth                                 | 250-300<br>(450MHz                     | 300 MHz               | MHz     |

| Read Out time for an event<br>(2 gains 16 cells) | < 1.5                                  | <2                    | μS      |

| Fixed Pattern noise                              | 0.4                                    |                       | mV rms  |

| Total noise (constant with<br>frequency)         | 0.65<br>(0.5mV if<br>FPN<br>cancelled) | <0.8                  | mV rms  |

| Maximum signal (limited by<br>ADC range)         | 2<br>(4)                               | 2                     | V       |

| Dynamic Range                                    | >11.6<br>(12.6)                        |                       | bits    |

| Crosstalk                                        | <3                                     | <3                    | per mil |

| Integral non linearity                           | < 1                                    | <1                    | %       |

| Sampling Jitter                                  | <15                                    | <50                   | ps rms  |

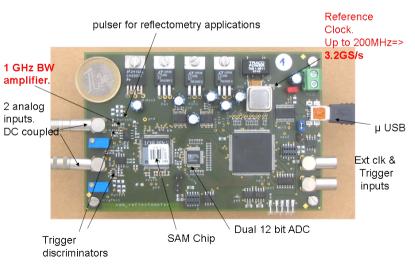

#### SAM chip

#### **Blue: on HESS2 FE boards.** Red: on the USB test board

JF. Glicemsteider the NEOFAr team?

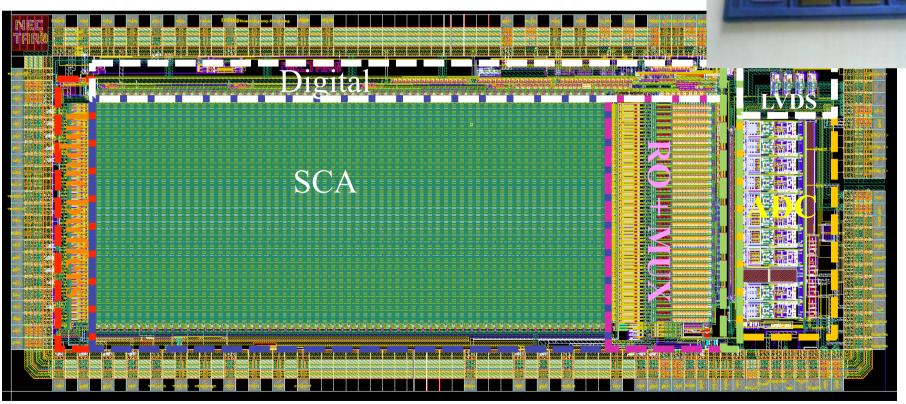

# Nectar O chip Layout

- CMOS AMS 0.35µm technology.

- 3x7mm chip size

- final chip could integrate 4 diff channels on a 5mm\*7mm chip

- chip returned from foundry in July, is tested right now.

JF. Glicenstein (for the NECTAr team)

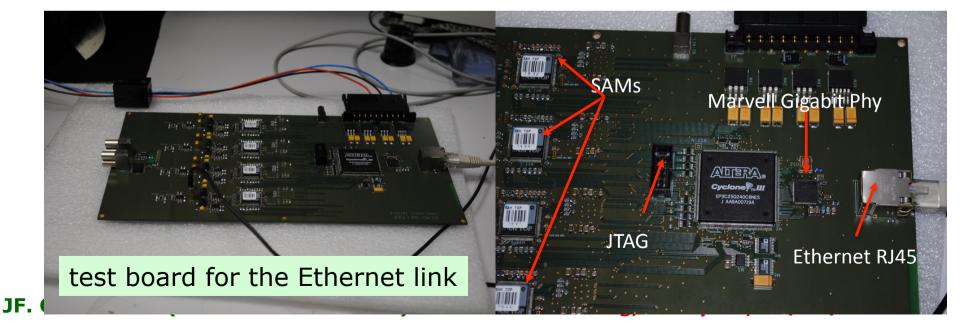

## Front-end FPGA

- Integrates:

- FE control

- Event FIFOs

- Ethernet Interface

- Ethernet Interface:

- 100 Mbits/s or 1 Gbit/s

- in a low cost FPGA (~ 30 €)

- uses UDP protocol instead of TCP

- commercial IP

P.Nayman *LPNHE*

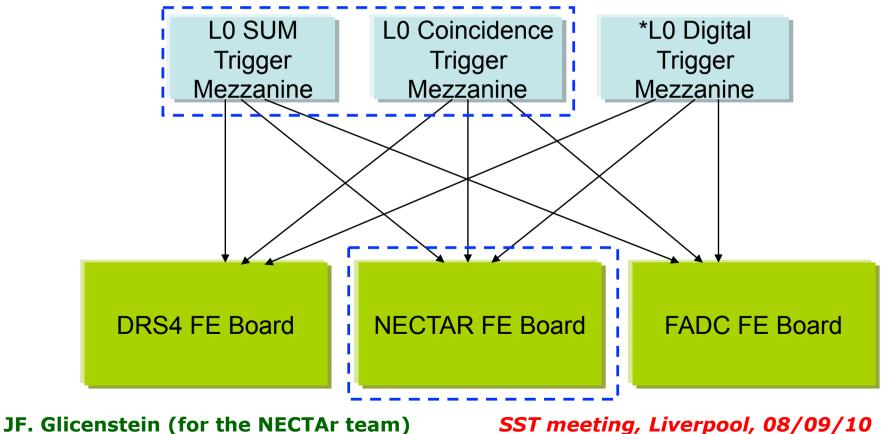

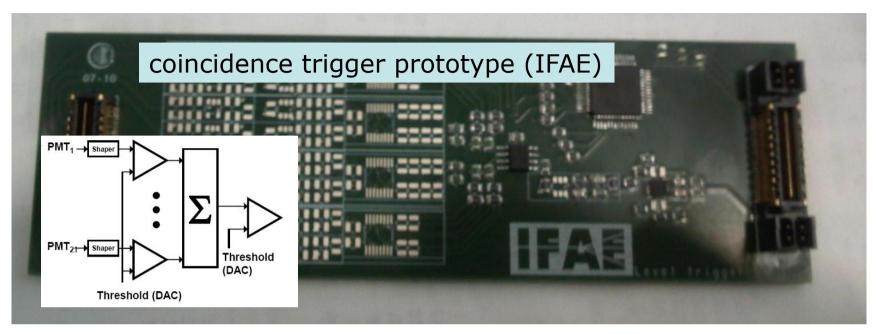

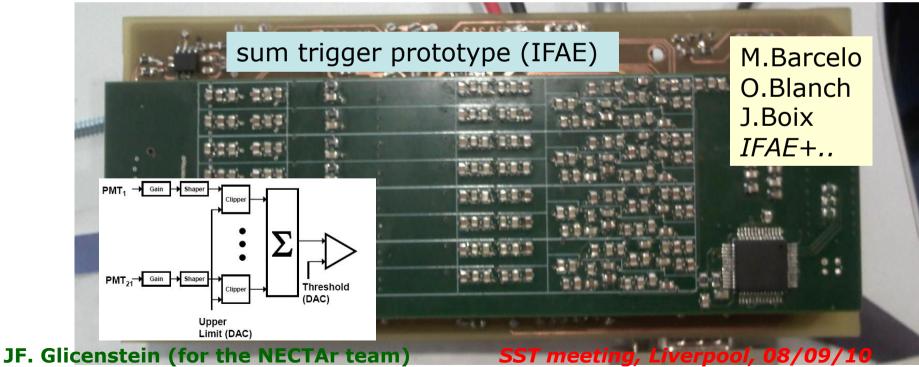

# LO trigger (analog)

- Prototypes designed at IFAE

- Well known Trigger concepts:

- Coincidence of Pixels above threshold (HESS)

- SUM Trigger (MAGIC)

- Built two Trigger mezzanines for tests with Front End Board

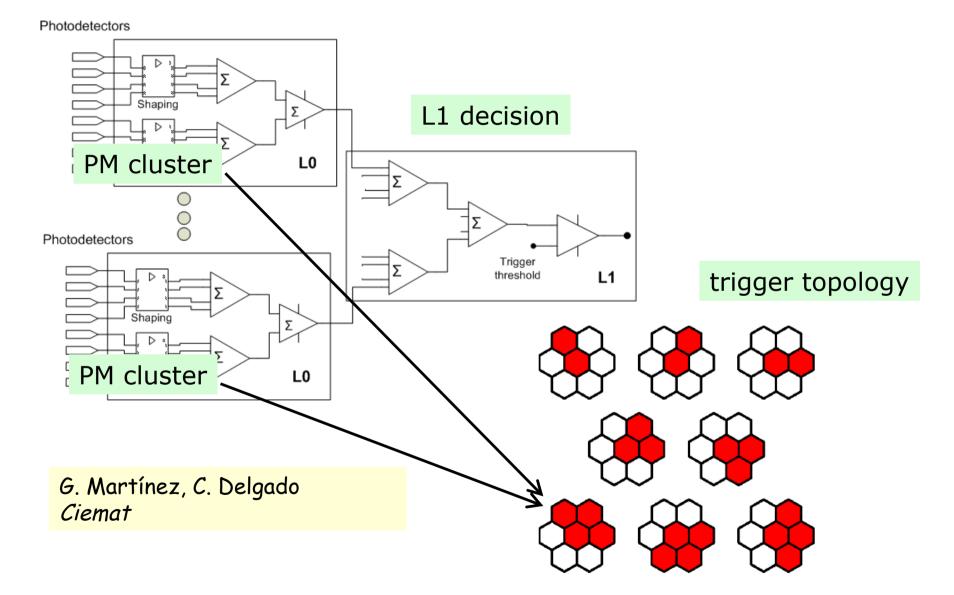

# L1 trigger

JF. Glicenstein (for the NECTAr team)

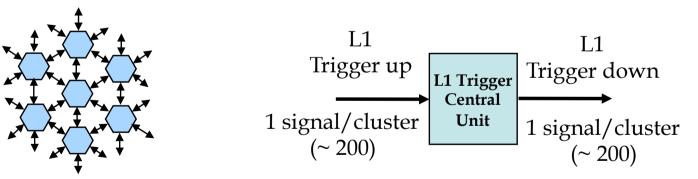

#### L1 trigger implementation

#### Two approaches for the L1 logic and distribution:

Without central unit:

Any cluster can start the distribution of L1 trigger to a certain region of interest or the whole camera

With central unit:

A central unit collects L1 outputs from all cluster and distributes L1 trigger down to a certain region of interest or the whole camera

The L1 decision can be forwarded to a ROI or the whole camera.

G. Martínez, C. Delgado Ciemat SST meeting, Liverpool, 08/09/10

JF. Glicenstein (for the NECTAr team)

## Conclusions and outlook

- HV design: design by ISEG expected in October

- Amplifier (UCB), NECTArO returned from foundry in July

tests started, results are promising

- FPGA ethernet readout OK

- L0 Trigger mezzanines prototypes available

- If all of the above OK, full camera module built end 2010/beginning 2011