A Fast CCD Vertex Detector for the Future e<sup>+</sup>e<sup>-</sup> Linear Collider: Some Recent Developments

Tony Gillman Rutherford Appleton Laboratory

### on behalf of The LCFI Collaboration

## Outline

### Introduction

- CCDs are ideal candidates for vertex detectors in the linear collider environment

- In SLD they have already demonstrated (with 1990s technology):

- Excellent 2-d space-point resolution ~3.5μm

- Very small layer thickness (0.4% X<sub>0</sub> in SLD) → low multiple scattering

- Serial readout multiplexes data by 200,000:1 → negligible signal cable plant

- Si-processing technology is still advancing rapidly:

- ◆ → Faster clocking

- $\bullet \rightarrow$  Improved signal/noise performance

- → Larger area devices

- A conceptual design for a CCD-based VXD for the future linear collider has already been presented

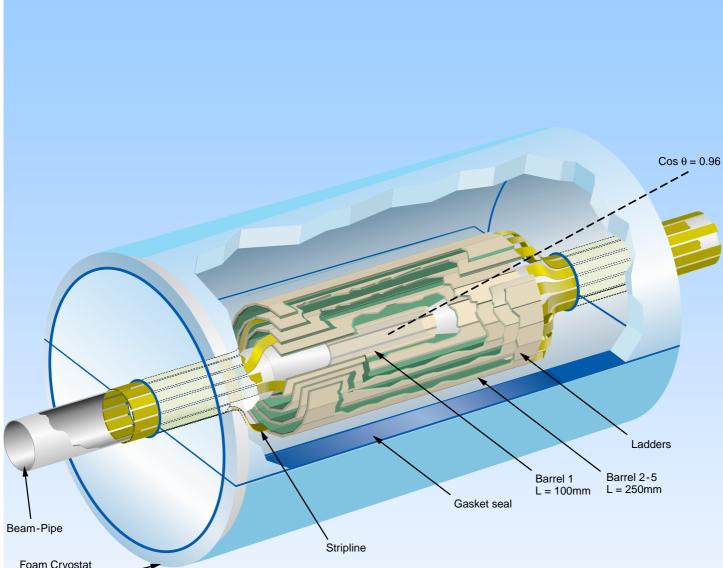

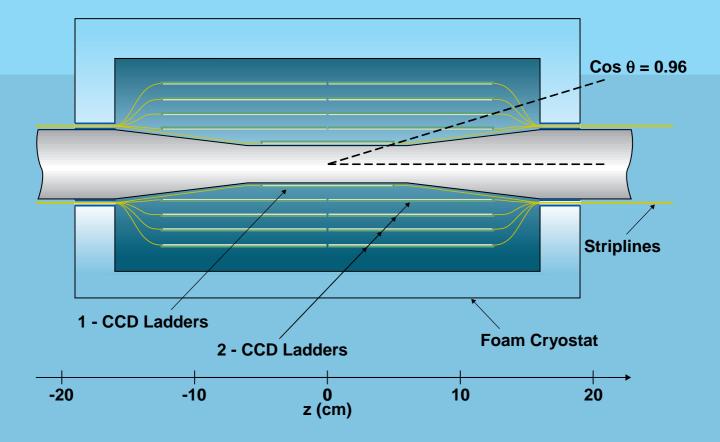

## **CCD VXD for the Future Linear Collider**

Foam Cryostat and Faraday Cage

| Detector performance targets                                                                             |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                                          |  |  |  |  |  |  |

| <ul> <li>5-barrel construction to provide redundant stand-<br/>alone tracking</li> </ul>                 |  |  |  |  |  |  |

| Inner barrel (B1): radius 15 mm — length 100 mm                                                          |  |  |  |  |  |  |

| • 3-hit acceptance (including B1) to $\cos \Theta = 0.96$                                                |  |  |  |  |  |  |

| <ul> <li>Individual layer thickness</li> <li>0.06% X<sub>0</sub></li> </ul>                              |  |  |  |  |  |  |

| Dimensions of largest CCD 125 x 22 mm <sup>2</sup>                                                       |  |  |  |  |  |  |

| Pixel readout rate 50 MHz                                                                                |  |  |  |  |  |  |

| <ul> <li>Neutron radiation tolerance 10<sup>10</sup> n cm<sup>-2</sup><br/>(1 MeV-equivalent)</li> </ul> |  |  |  |  |  |  |

### Current R&D programme

Initially (first 3 years) focussed on 3 main areas:

High-speed CCD clocking — up to 50 MHz

Techniques for low-mass ladder assemblies

Neutron irradiation studies

At a later stage:

Real-time signal processing (min-l clusterfinding) using fast FPGA-based algorithms

Customised CCD design:

column-parallel architectures

two-phase gate structures

Iow-noise output circuitry

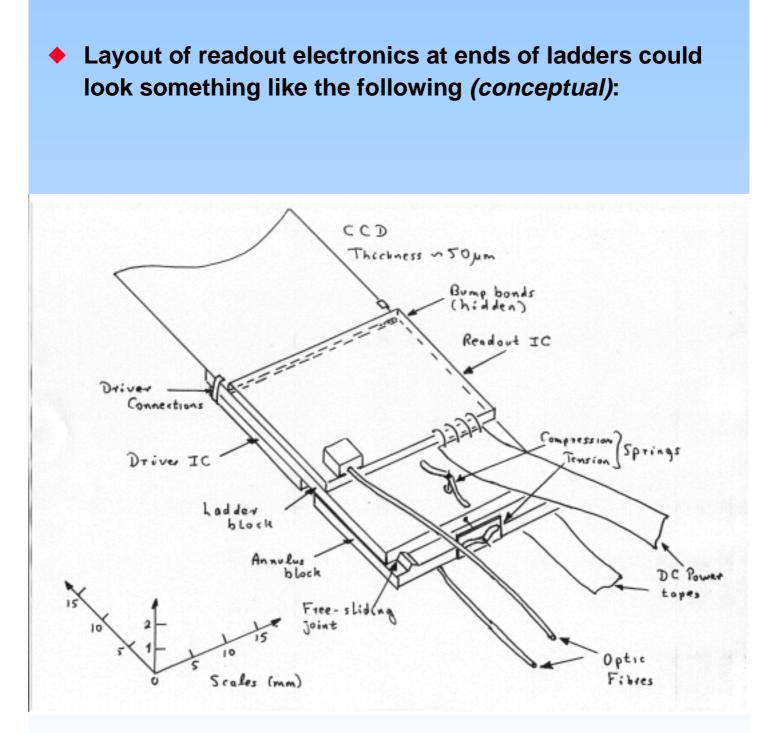

Electronic system design:

clocking and signal processing electronics integrated with CCDs

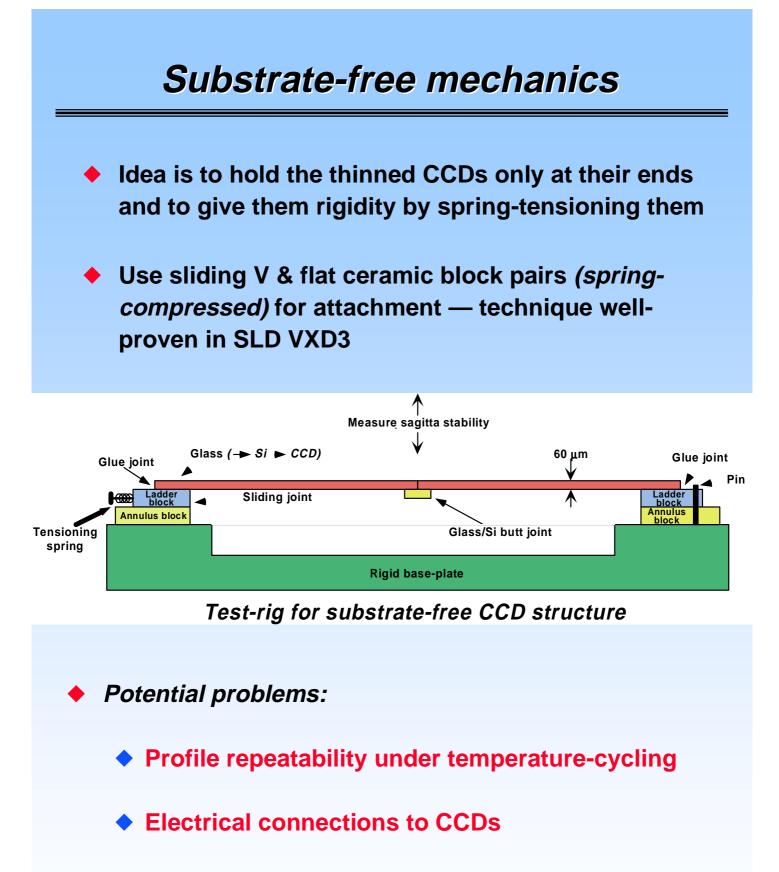

### **Mechanical studies**

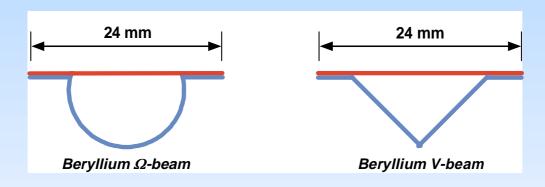

Minimal layer thickness is crucial for precision vertexing (multiple scattering)

Early studies assumed thin CCDs mounted on one side only of a thin Be substrate strengthened by Ω or V beam technique (total thickness ~250 µm):

The CCDs would be thinned to the edge of the epitaxial layer by lapping and etching — ~30 μm

This would give ~0.12% X<sub>0</sub> per layer — of which the Be and associated adhesive contributes 0.09% X<sub>0</sub>

Could the Be support structure be eliminated?

• We are investigating an unsupported-Si technique

- Back-face metallisation for ground-plane difficult

- Handling!

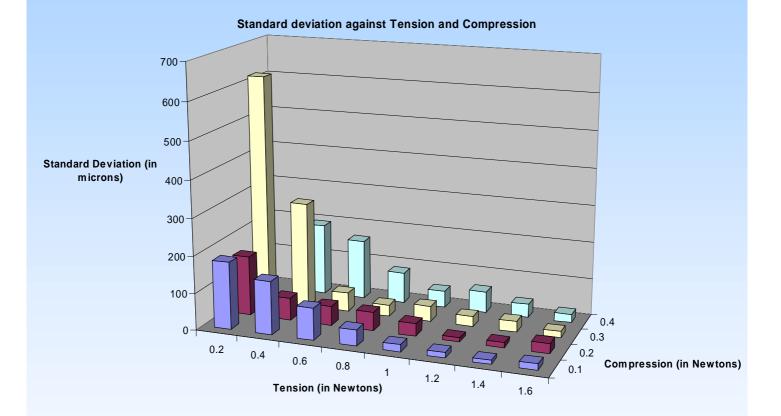

### S/S-free mechanics — initial results ...

Sagitta value measured 20 times for each combination of spring compression and tension, physically disturbing system between measurements

Comments:

• Tensioning spring too weak  $\rightarrow \sigma$  ~few tens of  $\mu m$

# S/S-free mechanics — initial results ...

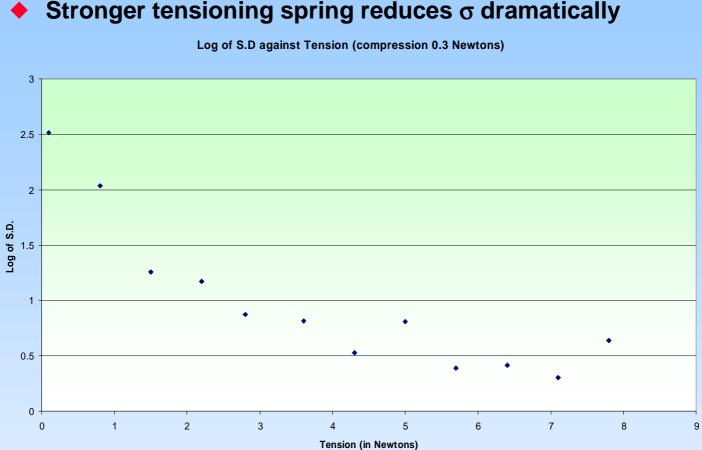

#### Stronger tensioning spring reduces $\sigma$ dramatically

(Tentative) conclusions:

- The technique appears to work  $\sigma \rightarrow$  ~3  $\mu m$  for spring tension >5 N

- The annulus blocks could be made from better surface-finish ceramic

More studies are needed, particularly at low-T ...

Further idea — could the Be beam-pipe thickness be reduced locally ... to 250 µm?

use VXD support shell for strain relief

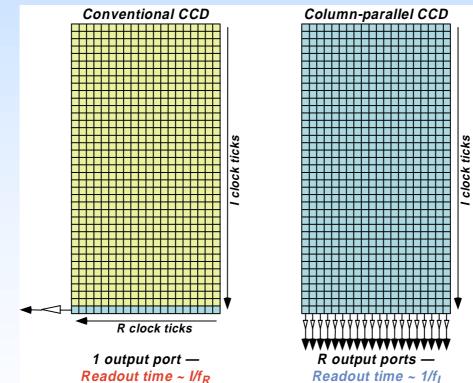

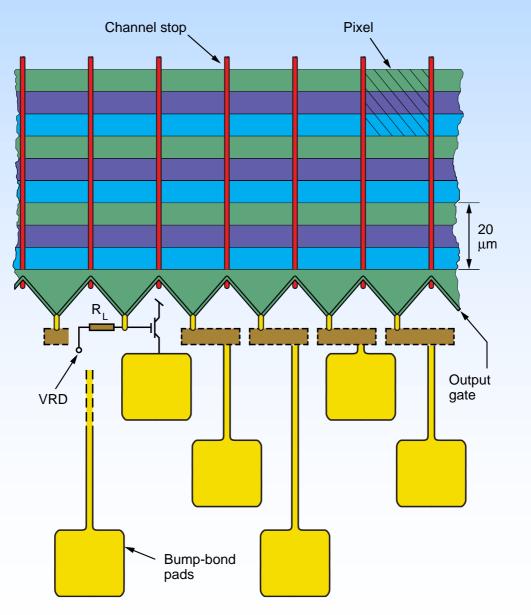

### Column-parallel CCD architecture

- In X-band LC, B1 CCDs (*r* = 12 mm) must be fully read out between bunch trains (8.3 mS) → 50 MHz clocking

- ◆ 100 bunches/train generates ~10 hits/mm<sup>2</sup> per CCD from e<sup>+</sup>e<sup>-</sup> pair background (3T field) → ~0.4% pixel occupancy

- In TESLA, read-out *between* bunch trains would integrate ~2800 bunches → ~20% pixel occupancy

- Solution increase *effective* clocking rate to >1 GHz by eliminating CCD serial (R) register and read out *during* bunch train

Consider area CCD as many linear CCDs reading out in parallel → 50 MHz I clock rate for ~1% pixel occupancy

This provides a few interesting technical challenges ...

- Can the CCD I-gates be clocked at 50 MHz with good drive waveforms across entire imaging area — essential for good charge transfer efficiency?

- Is the resultant in-cryostat power dissipation too high to be managed with modest cold gas flow rates?

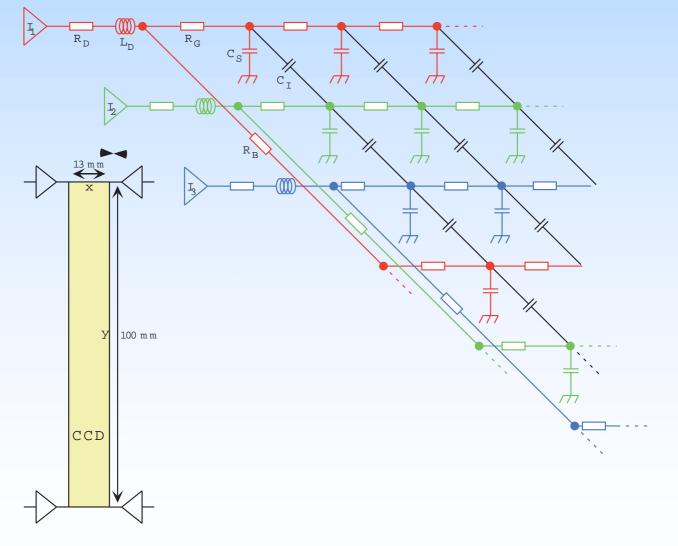

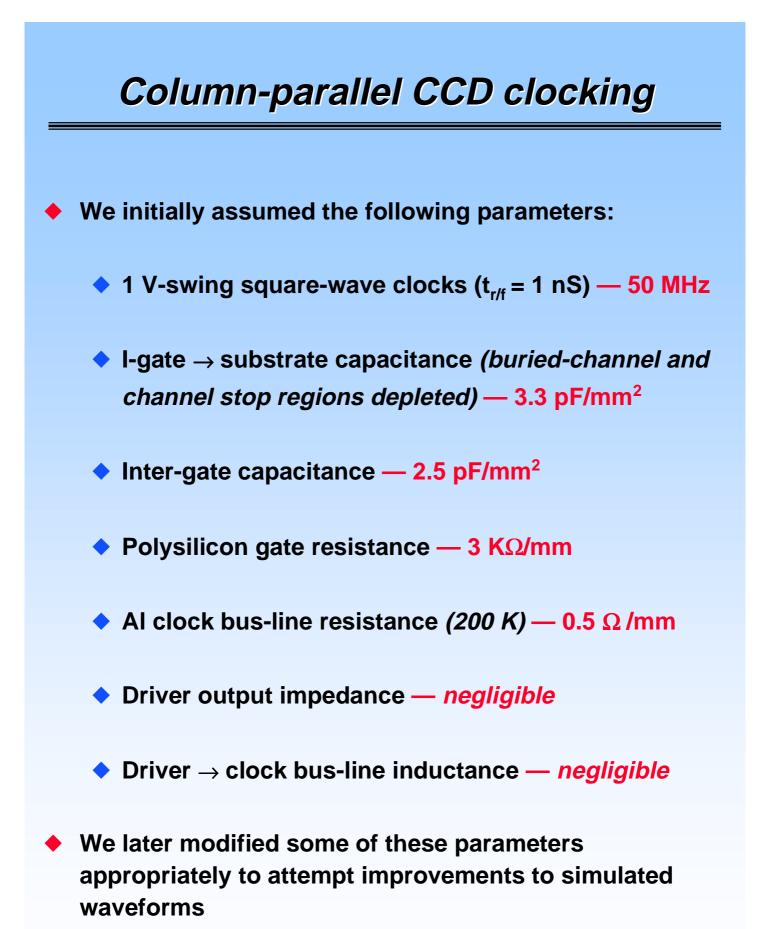

- We have modelled a realistic inner-layer CCD with SPICE, using Marconi-approved parameters:

SPICE model of column-parallel CCD gate structure (VXD layer 1 dimensions)

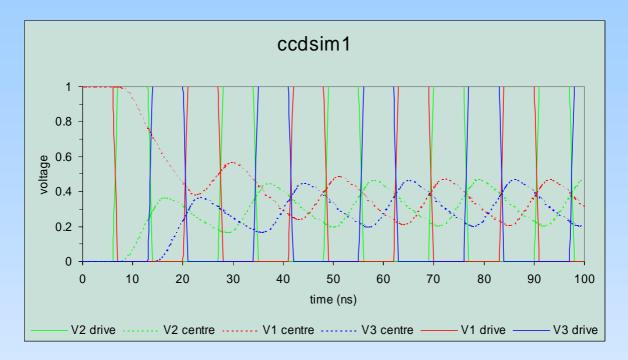

Starting with these nominal parameters we monitor waveforms at extreme points on the gate structure

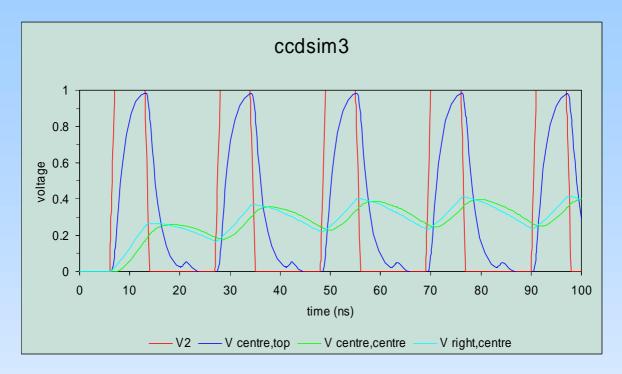

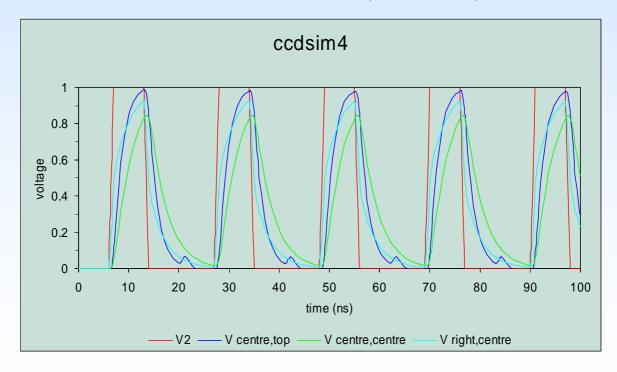

### a) Drive waveform variation across the CCD in X:

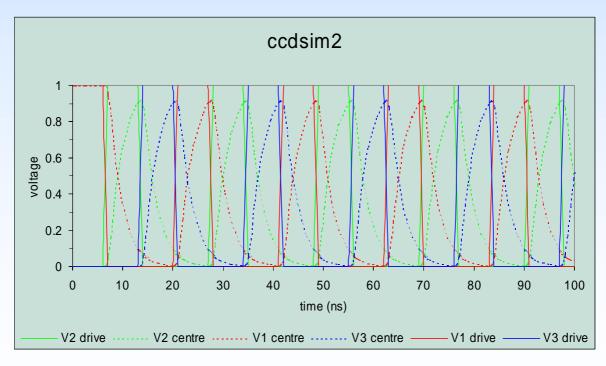

#### Add 3 $\mu\text{m}$ wide Al overlay to the polysilicon gates —

Waveform amplitudes attenuated by <10% in centre (X)</p>

### b) Drive waveform variation along the CCD in Y:

Thicken the AI bus-lines from 1  $\mu$ m  $\rightarrow$  10  $\mu$ m —

Waveform amplitudes attenuated by <15% in centre (Y)</p>

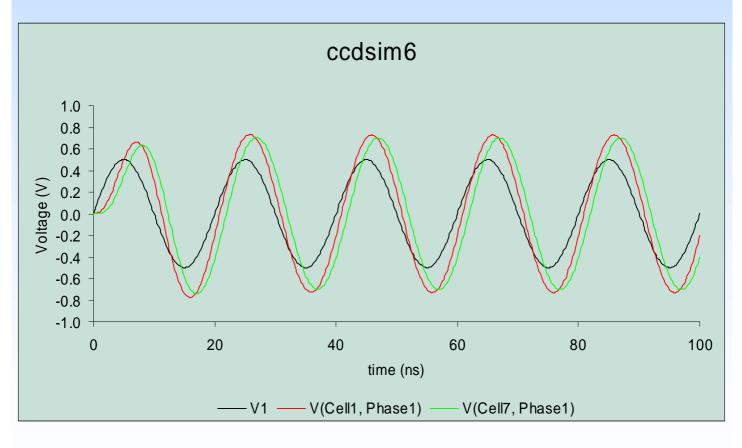

- c) Move to a 2-phase gate structure with sinusoidal drive waveforms (scale all parameters accordingly and add inductance in the clock driver connection):

- Advantages:

- Lowest possible driver frequency spectrum

- Reduced peak current demands on drivers

- Balanced anti-phase drive waveforms should produce minimal crosstalk to CCD output signals

### Waveforms in centre (X) of CCD have ~1.5% attenuation with ~1 nS phase lag

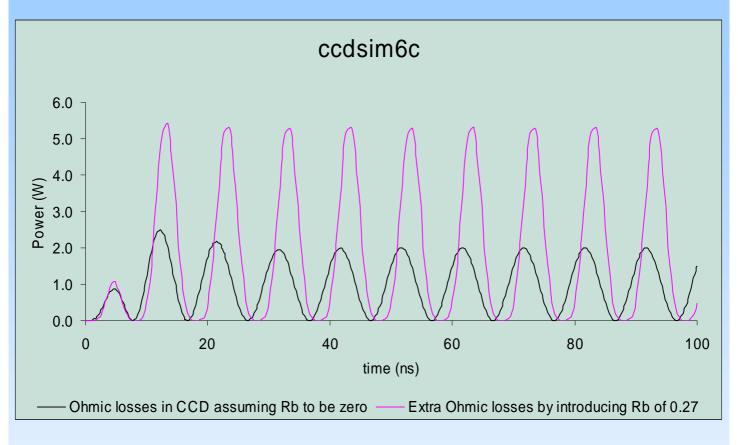

### d) Clocking power dissipation (resistive) per CCD:

- Total power dissipation/CCD ~3.6 W (1 V p-p clocks)

- N.B. Freezing clocking between TESLA bunch trains reduces power dissipation by a further factor of 200

- For layer 1 of the VXD mean P<sub>D</sub> <150 mW

- ◆ CCDs in outer layers can be clocked at a lower frequency (*much smaller backgrounds*) — → Total VXD power dissipation ~few watts

- Further simulation work needed (ISE TCAD)

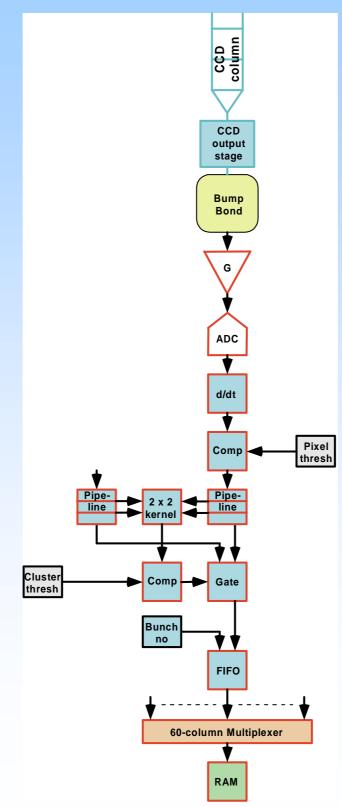

# **Column-parallel CCD signal-handling**

- Simplify reset circuit passive with resistive load

- Signal-processing (digitisation, real-time cluster-finding) performed adjacent to CCD — in local readout chip

- 1-d row of staggered bump bonds (industry-standard) interconnects CCD and readout chip — 60 μm pitch

- Sparsified data transmitted off detector by optical fibre(s)

## Column-parallel CCD signal-handling

### Column-parallel CCD signal-handling

Functionality of readout chip (n.b. very preliminary ideas — more study needed):

### Column-parallel CCD data rates

- Proposal is to read out the CCDs throughout the 950 μs bunch train, storing *sparsified* cluster data in local RAM

- Based on current background rate estimates for TESLA, we would expect the following (per bunch train):

| <u>Layer</u> | <u>CCD mm<sup>2</sup></u> | Ladders/CCDs | <u>Clk/T<sub>RO</sub></u> | Hits/mm <sup>2</sup> | <u>Σ backgrnd</u> |

|--------------|---------------------------|--------------|---------------------------|----------------------|-------------------|

| 1            | 100x13                    | 8/8          | 50MHz/50μs                | 5.9                  | 1165 K            |

| 2            | 125x22                    | 8/16         | 25MHz/250μs               | 2.9                  | 484 K             |

| 3            | 125x22                    | 12/24        | 25MHz/250μs               | 1.1                  | 276 K             |

| 4            | 125x22                    | 16/32        | 25MHz/250μs               | 0.9                  | 301 K             |

| 5            | 125x22                    | 20/40        | <b>25MHz/250</b> μs       | 0.6                  | 251 K             |

- Total no of hits to store during bunch-train ~2.5 x 10<sup>6</sup>

- Each hit can contain up to 4 pixels (2 x 2 clusters) and must also be address-tagged → 6 bytes/hit

- Data volume to store during bunch-train ~15 Mbytes

- On receipt of a trigger, only data corresponding to 1 subsequent frame from each CCD need to be retained, so data volume to be transferred off the detector before next bunch-train is reduced to ~2.1 Mbytes per event

- For a trigger rate <50 Hz (!), data to transmit off detector</li>

~21 Mbytes per bunch-train → 1 optical fibre per end!

- N.B. If data storage cannot be on-detector, <u>all</u> sparsified data must be exported → 1 – 4 optical fibres per CCD

## Conclusions

- Initial results just emerging are very encouraging:

- Substrate-free mechanics appears viable

- Simulations show that clocking a column-parallel structure at 50 MHz is feasible — waveform integrity and power are both acceptable

- The column-parallel architecture makes CCDs fullycompatible with the TESLA environment

- There are new ideas for in-detector signal processing, data sparsification and post-trigger processing

- CCD radiation damage studies are being prepared

- A close involvement with CCD designers/manufacturers is maintained, and is crucial