# Vertex Detectors: The State of the Art and Future Prospects

C J S Damerell

December 1995

# VERTEX DETECTORS: THE STATE OF THE ART AND FUTURE PROSPECTS

C J S Damerell

**Rutherford Appleton Laboratory**

Chilton, Didcot, OX11 0QX, England

#### **ABSTRACT**

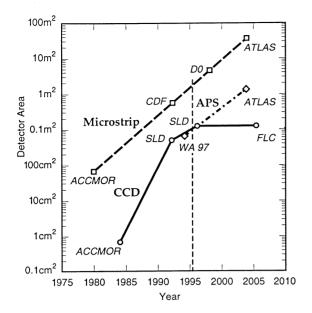

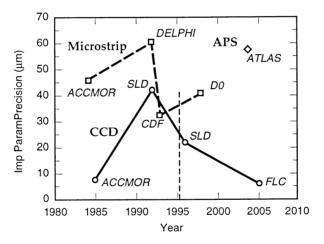

We review the current status of vertex detectors (tracking microscopes for the recognition of charm and bottom particle decays). The reasons why silicon has become the dominant detector medium are explained. Energy loss mechanisms are reviewed, as well as the physics and technology of semiconductor devices, emphasising the areas of most relevance for detectors. The main design options (microstrips and pixel devices, both CCDs and APSs) are discussed, as well as the issue of radiation damage, which probably implies the need to change to detector media beyond silicon for some vertexing applications. Finally, the evolution of key performance parameters over the past 15 years is reviewed, and an attempt is made to extrapolate to the likely performance of detectors working at the energy frontier 10 years from now.

Lectures Presented At the Twenty Third Annual Summer Institute

On Particle Physics

SLAC, Stanford, California 94309

July 10-21, 1995

### TABLE OF CONTENTS

| 1 | Introd                                                  | uction 1                                                                                                                                                                                                                                                                           |                                              |  |

|---|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| 2 | Energy Loss of High Energy Charged Particles in Silicon |                                                                                                                                                                                                                                                                                    |                                              |  |

|   | 2.1<br>2.2<br>2.3<br>2.4                                | Simplified Treatment Improved Treatment Implications for Tracking Detectors Summary                                                                                                                                                                                                |                                              |  |

| 3 | Physics and Properties of Semiconductors                |                                                                                                                                                                                                                                                                                    |                                              |  |

|   | 3.1<br>3.2<br>3.3                                       | Conduction in Pure and Doped Silicon The <i>pn</i> Junction Charge Carrier Transport in Silicon Detectors                                                                                                                                                                          | 13<br>21<br>28                               |  |

| 4 | Microstrip Detectors                                    |                                                                                                                                                                                                                                                                                    |                                              |  |

|   | 4.1<br>4.2<br>4.3                                       | Introduction The generic microstrip detector Microstrip detectors: detailed issues 4.3.1 Design optimisation 4.3.2 Spatial precision in microstrip detectors 4.3.3 Electronics for Microstrip Detectors Physics performance and future trends                                      | 30<br>31<br>34<br>34<br>38<br>40<br>44       |  |

| 5 | Pixel-Based Detectors                                   |                                                                                                                                                                                                                                                                                    |                                              |  |

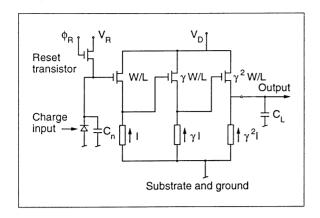

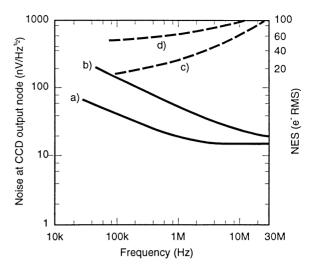

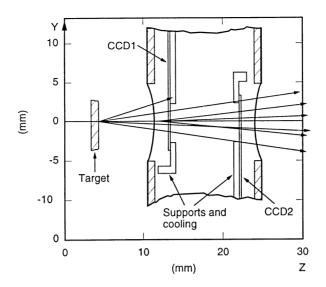

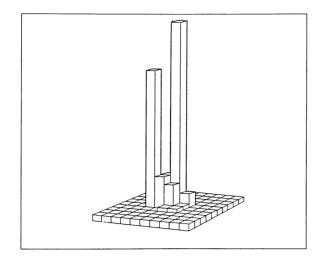

|   | 5.1<br>5.2                                              | Introduction Charge-Coupled Devices (CCDs) 5.2.1 Structure and Basic Operation 5.2.2 CCD Charge Transfer and Readout; Detailed Issues 5.2.2.1 Charge Transfer Process 5.2.2.2 Charge Detection 5.2.2.3 Vertex Detector Readout Options 5.2.3 Physics Performance and Future Trends | 47<br>49<br>50<br>56<br>56<br>58<br>60<br>63 |  |

|      | 5.3      | Active                             | Active Pixel Sensors (APSs)          |     |  |  |

|------|----------|------------------------------------|--------------------------------------|-----|--|--|

|      |          | 5.3.1                              | Design Options                       | 70  |  |  |

|      |          |                                    | 5.3.1.1 Monolithic Detectors         | 70  |  |  |

|      |          |                                    | 5.3.1.2 Hybrid Detectors             | 71  |  |  |

|      |          | 5.3.2                              | Performance and Future Trends        | 72  |  |  |

| 6    | Radia    | tion Damage in Silicon Detectors 7 |                                      |     |  |  |

| 6.1  | Introd   | Introduction                       |                                      |     |  |  |

|      | 6.2      | Ionizing Radiation                 |                                      |     |  |  |

|      | 6.3      | •                                  | cement Damage                        | 75  |  |  |

|      | 6.4      |                                    | or-Specific Effects                  | 79  |  |  |

|      |          | 6.4.1                              | Microstrip Detectors and APS Devices | 79  |  |  |

|      |          |                                    | CCDs                                 | 80  |  |  |

|      |          |                                    | Local Electronics                    | 84  |  |  |

|      | 6.5      | Future                             | Prospects                            | 85  |  |  |

| 7    | Beyo     | Beyond Silicon                     |                                      |     |  |  |

|      | 7.1      | Galliur                            | n Arsenide Detectors                 | 86  |  |  |

|      | 7.2      | CVD                                | 87                                   |     |  |  |

|      | 7.3      | Local Electronics                  |                                      |     |  |  |

| 8    | Conc     | usions                             |                                      | 90  |  |  |

| Ackn | owledg   | ements                             |                                      | 94  |  |  |

| Abbr | eviation | S                                  |                                      | 95  |  |  |

| Syml | bols     |                                    |                                      | 96  |  |  |

| Refe | rences   |                                    |                                      | 100 |  |  |

#### 1 Introduction

There is for me a considerable sense of nostalgia in giving these lectures, since I previously gave such a series at the Summer Institute of 1984, which was especially noteworthy since it was coupled with the Pief-Fest to mark the retirement of Panofsky as Director of SLAC. Younger readers will be surprised to learn that the 1984 Institute, on the theme of the sixth quark, included evidence for the discovery of top with a mass of  $40 \pm 10 \text{ GeV}$ .

In my 1984 lecture series, I suggested that these candidate top events really needed additional experimental evidence in order to be proved or disproved, and that this would best be provided by a precision vertex detector able to resolve the associated B decays. At the time, this suggestion was not taken particularly seriously. A lecture series relating to experimental methods of heavy quark detection at the same Institute made no mention of vertex detectors. Detectors with the required precision were only beginning to be used in the fixed target regime, and many of these were based on technologies such as bubble chambers that were manifestly not applicable to the collider environment. My own lectures made mention of techniques which have subsequently fallen into disuse for this reason. However, my main aim in those lectures was to establish a case for silicon vertex detectors in the collider environment. Our community was at that time in the early stages of planning the LEP and SLC detectors, and I focused particularly on  $Z^0$  decays as the firm ground on which to base the case for these silicon vertex detectors. One was heavily dependent on Monte Carlo simulations of events with heavy flavour decays, where the possibilities for flavour tagging and some measure of topological vertexing could be demonstrated. Physicists at the time could be forgiven for not being wholly convinced by these simulations. Silicon detectors in those days were limited in size to a few square centimetres, were typically serviced by a huge amount of local electronics (easily accommodated in a fixed target experiment, but completely excluded in a collider), and detector reliability was a major problem. Here again, access for servicing which was easy in the fixed target environment would become much more difficult at the heart of a hermetic collider detector. In 1984, these Monte Carlo studies left on one side a host of technical problems which required many years of hard work to solve. Due to the loosely coupled R&D projects of many collaborations, the progress made since then has been immense. We now have a large variety of silicon vertex detectors in use in fixed target as well as collider experiments around the world. New designs are constantly being fabricated, and tried out in test beams. The associated local electronics has shrunk spectacularly and at the same time become much faster and more powerful.

My task is thus made easier than eleven years ago; silicon vertex detectors have become well established within the standard toolkit of high energy experiments. I no longer need rely on Monte Carlo studies to prove their usefulness; we can just look at the data. On the other hand, the array of detector types available has become somewhat bewildering, and I shall aim to provide some systematic guidance for non-experts. Furthermore, despite the fact that the proponents of silicon detectors have been able to expand their horizons, even planning in some case to displace gaseous tracking detectors with tens of square metres of strip detectors, they have begun to run into serious challenges in some vertex applications. In various hadron beam experiments, most

spectacularly at LHC at its design luminosity, silicon detectors as we now know how to build them will fail after an unacceptably short time, when placed close to the interaction region. This has stimulated a major effort with other materials of greater radiation resistance, as we shall see towards the end of these lectures.

We are seeing the beginning of a technology division between  $e^+e^-$  colliders and hadron colliders, in regard to vertex detection at the energy frontier. Both are well suited to the use of silicon at large radii, for general purpose tracking. But it is likely that at the luminosities needed for 'discovery physics' at the TeV energy scale, silicon detectors will continue to be useful for high resolution vertex studies in the  $e^+e^-$  collider environment but not at LHC.

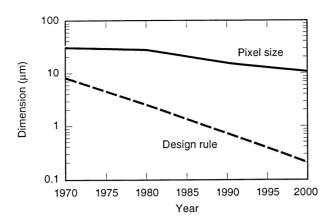

There are clearly great advantages in remaining with the silicon technology as far as possible. A major reason for its rapid growth as a material for tracking detectors is that the *planar process* for manufacturing silicon integrated circuits has been developed to an extremely fine art. These developments are continuing at a pace which reflects the billions of dollars annually invested, for purposes which have nothing to do with scientific research let along particle physics.

Before plunging into our rather specialised topic in fine detail, it is useful to take a brief look at the overall scene of silicon devices, particularly regarding their utility as radiation detectors. For, unlike some detection materials which are not widely used outside of our field (e.g. liquid argon) silicon finds applications in a vast range of scientific sensors. We are in particle physics concerned with its use for tracking microscopes that allow us to probe the smallest and shortest lived particles in nature. Silicon devices also provide the means to see the largest and oldest structures in the universe. Between these extremes, these sensors find a vast number of diverse applications, some of great importance to mankind (e.g. in medical imaging). Technically, all these areas are closely linked, so progress in one field may be significant to many others. All these scientific applications are dwarfed by the use of silicon sensors in the mass consumer markets, notably in video cameras but with applications now extending into other areas. What makes this field particularly dynamic is the flow of ideas from people with very different aims and agendas. The next major advance for HEP detectors may come from an astronomer concerned about radiation damage to his space-based telescope, or from the designer of an output circuit able to function at HDTV readout rates. Similarly, those designing devices for HEP use, may dream up an advance that happens to be much more significant for some other field.

Why is silicon the preferred material for high precision tracking detectors, as well as for such a wide range of radiation detectors?

Firstly, a condensed medium is essential if point measurement precision below about 10  $\mu$ m is required. Gaseous tracking detectors are limited by diffusive spreading of the liberated electron cloud to precision of typically some tens of microns. Such detectors are entirely adequate for a host of particle tracking applications, but not for precision vertex detectors. Having established the need for a condensed medium, one should in principle consider liquids. There was some work done on high precision liquid xenon tracking detectors in the '70s [1] but there were many problems, not least of which was maintaining purity in conditions where the high

mobilities of many contaminants rendered them particularly potent. In contrast, silicon wafers refined to phenomenal purity levels can then be sawn, exposed to the atmosphere, and assembled in complex geometries, with no degradation of their bulk electron lifetime characteristics. For these reasons, silicon and other solids are generally to be preferred, as opposed to liquids, for high precision tracking purposes. There are, however, many possible solid state detection media, so why pick silicon?

Silicon has a band gap of 1.1 eV, low enough to ensure prolific production of liberated charge from a minimum-ionizing particle, hereafter referred to as a MIP, (about 80 electron-hole pairs per micron of track length) but high enough to avoid very large dark current generation at room temperature (kT) at room temperature = 0.026 eV). Being a low Z element of excellent mechanical properties (high modulus of elasticity) makes silicon an ideal material for use in tracking detectors where multiple scattering is of concern. This is nearly always the case in vertex detectors where tracks need to be extrapolated to the interaction region, and the dynamics of the fragmentation process ensures that even at the highest CM energies, many of the particles produced are of relatively low energy.

Besides these detector-related reasons, one has the vast IC technology developed specifically for this material. Silicon is currently unique in the combination of assets it brings with it; the growth of huge crystals of phenomenal purity, the possibility of *n*- and *p*-type doping, the possibility of selective growth of highly insulating layers (SiO<sub>2</sub> and Si<sub>2</sub>N<sub>3</sub>), and the possibility of doing all these using microlithographic techniques, allowing feature sizes of around 1 micron (and falling with time). A very readable account of the remarkable human stories associated with these amazing developments is to be found in George Gilder's book on the subject [2]. Very small feature sizes are of course precisely what one requires in order to construct detectors of precision below 10 microns. Overall, the art of producing integrated circuits is probably by far the most sophisticated, fastest developing area of technological growth in the history of mankind. Without these developments, silicon as a detector of nuclear radiation would have remained a minor player, subject to arcane production procedures, of limited use for the spectroscopy of low energy gamma rays, and wholly inappropriate for particle tracking purposes.

Though the scientific applications are of great importance, they are dwarfed by the use of silicon detectors for mass market consumer products and commercial interests. Accurate figures are not readily available, but it seems that approximately \$100M per year is spent on R&D of CCDs for domestic video and still cameras. These are interline transfer devices of no direct use for most scientific imaging applications. About \$10M is spent on CCD development for medical and other scientific imaging applications (mostly X-rays). Silicon devices specifically aimed at particle tracking (microstrip detectors, CCDs and active pixel sensors, hereafter referred to as APS devices) probably attract only \$1M (order of magnitude) in R&D per year.

Even the consumer market for silicon sensors is dwarfed by the really hot commercial areas. For example, it was recently reported that NEC demonstrated a 1 Gbit DRAM. Production devices are expected to follow in three year's time, after the expenditure of *a further* \$1.5B of R&D funding. Much of this will go in the development of sub-micron manufacturing capability, which ultimately will benefit the particle physics

instrumentation community. We can eventually look forward to *sub-micron* tracking precision with *sub-nanosecond* timing information. However, the pace of such developments will be determined by the major players outside our own field, and there will inevitably be a time lag of several years between a technology being available for mass produced ICs and it being affordable for our purposes.

While the silicon processing infra-structure and R&D for a specific device can be enormously expensive, once production begins the costs can be modest. The ingredients of integrated circuits (sand, air, aluminium) are ridiculously cheap, and this benefit can be seen dramatically in large production runs. For example, SONY produce approximately 5 million CCDs per year for the domestic video camera market, at a production cost of only around \$10, including the micro-lens and colour filter system. This is a truly amazing achievement, as you can convince yourself by just looking through a microscope at one of these devices.

In summary, the match between silicon (and its attendant technologies) to the aspirations of the experimentalist wishing to construct tracking detectors of the highest possible precision, is evident. Were it not for the problems of radiation damage (which are most serious in the context of hadron colliders), there is little doubt that our field would by now have standardised completely on this material for vertex detection. Some time ago, test devices even surpassed photographic nuclear emulsions in precision, and with all the advantages of electronic readout. The challenge of hadron machines has stimulated some brave souls to undertake the monumental task of achieving similar technical performance using more radiation resistant materials than silicon. They have of course to solve the problems not only of the detectors but also of the local electronics. We shall take a brief look at what they are doing in Section 7 of this paper. Other than that section, we shall devote ourselves exclusively to a discussion of silicon detectors and electronics.

# 2 Energy Loss of High Energy Charged Particles in Silicon

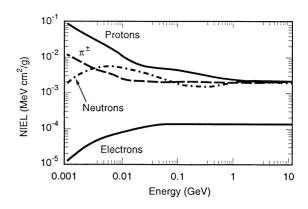

High energy charged particles traversing crystalline silicon can lose energy in two ways. Firstly, by ionization of the atomic electrons. This simple picture becomes rather more complex in regard to the valence electrons, as we shall see. The second energy loss mechanism (the so-called non-ionizing energy loss or NIEL) consists of displacement of silicon atoms from the crystal lattice, mostly by the process of Coulomb nuclear scattering. Only if the energy transfer to the nucleus exceeds approximately 25 eV can the atom be displaced from its lattice site. Below that, the energy is dissipated by harmless lattice vibrations. This implies an effective threshold energy for displacement damage with incident electrons (for example) of around 250 keV. Displacement of silicon atoms to *interstitial* positions (creating a *vacancy* in the lattice where the atom had previously been located) is one of the main radiation damage mechanisms. For a high energy particle, the fraction of energy loss going into the NIEL mechanism is relatively small, but the cumulative effects on the detector performance can be severe.

A detector placed in a neutron flux experiences no signal from primary ionization, but the interactions can cause a high level of NIEL in view of the large neutron-silicon scattering cross-section. For both charged hadrons and neutrons, other mechanisms of energy loss and radiation damage exist, notably neutron capture followed by nuclear decay, and inelastic nuclear scattering. The effects of non-ionizing energy loss on silicon detectors are considered in Section 6. In this section, we focus on the ionization energy loss only.

#### 2.1 Simplified Treatment

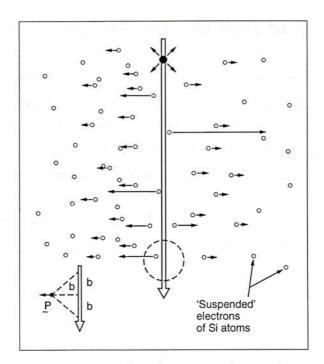

Let us first imagine all the atomic electrons to be free, as if the crystal consisted of the silicon nuclei neutralised electrically by a homogeneous electron plasma. As a charged particle traverses the material, it loses energy by collisions (Coulomb scattering) with the electrons. Close collisions, while rare, will result in large energy transfers, while the much more probable distant collisions give small energy transfers. The process can be thought of classically in terms of the impulse generated by the attractive or repulsive Coulomb interaction between the projectile and the electron. The nett impulse will be a kick transverse to the direction of travel of the projectile (see fig. 1). The greater probability of remote collisions arises simply from the greater volume of material available for collisions with a given impact parameter range, as the corresponding cylinder (of radius equal to the impact parameter) expands. In this simple case, the probability for a collision imparting energy *E* to an atomic electron is given by the Rutherford cross-section

$$\frac{d\sigma_R}{dE} = \frac{2\pi q_e^4}{m_e c^2 \beta^2} \times \frac{1}{E^2} \tag{2.1}$$

where  $q_e$  and  $m_e$  are the charge and mass of the electron.

Note the mass of the struck particle in the denominator. This explains why scattering off the silicon nuclei, which are much more massive, causes very little energy loss, though these collisions do make the major contribution to the deviation in angle of the incident particle trajectory, via the process of multiple nuclear

Fig. 1 Passage of charged particle through matter. Close collisions (electrons with small impact parameter b, shown by the inset) receive a powerful transverse impulse. Distant electrons receive a weak impulse.

Coulomb scattering. Also, for sufficiently large momentum transfers, these nuclear collisions contribute to the NIEL referred to above.

We are interested in evaluating the *mean* energy loss and also the *fluctuations*, for traversal of a given thickness detector. An apparently simple approach would be to perform the integration over all E to obtain the mean energy loss, and to run a Monte Carlo calculation with multiple traversals to determine the energy loss distribution (straggling formula). However, we see that the integral diverges like 1/E. The stopping power of this free-electron plasma would indeed be infinite, due to the long-range Coulomb interaction. In practice, the electrons are *bound* and this prevents very low energy transfers to the vast number of electrons which are distant from the particle trajectory. This divergence is conventionally avoided by introducing a semi-empirical cutoff (binding energy)  $E_{\min}$  which depends on the atomic number Z of the material. This is necessarily an approximate approach, since (for example) it ignores the fact that the outer electrons are bound differently in gaseous media than they are in solids. We shall need a more refined treatment to handle the cutoff in collisions with small energy transfer.

However, the Rutherford formula (with one small correction) is extremely useful as regards the close collisions, which are most important in defining the fluctuations in energy loss in 'thick' samples (greater than approximately 50  $\mu$ m of silicon, for example). The required correction is the upper cutoff  $E_{\rm max}$  in energy transfer imposed by the relativistic kinematics of the collision process. If the projectile mass is much greater than  $m_e$ , we have  $E_{\rm max} = 2m_ec^2\beta^2\gamma^2$ . Due to the  $1/E^2$  term in the Rutherford formula, we find that there is for each sample thickness, an energy transfer range in which the integrated probability of such transfers

through the sample falls from almost unity to nearly zero. The Poisson statistics on energy transfers in this range gives rise to fluctuations on the overall energy loss for each traversal. Thus the overall energy loss distribution consists of an approximately Gaussian core plus a high tail, populated by traversals for which a few close collisions occurred, each generating several times the mean energy loss. While the energy transfer region in which the probability function falls almost to zero is dependent on the sample thickness, this merely introduces an overall scale factor, so the *form* of the overall energy loss distribution is constant (the famous Landau distribution) over a wide range of detector thicknesses.

The rare close collisions with energy transfer greater than approximately 10 keV generate  $\delta$ -electrons of significant range, which may be important in tracking detectors due to their potential for degrading the precision. For these close collisions, all atomic electrons behave as if they are free and the Rutherford formula may be used with confidence.

For thin samples, the energy loss fluctuations are not adequately handled by the Rutherford formula with cutoffs  $E_{\min}$  and  $E_{\max}$ . In this case, the bulk of the energy loss arises from low energy transfer collisions for which the binding of the atomic electrons must be handled in detail. We shall now consider the improved treatment of this case, specifically for crystalline silicon, though the same principles apply in general.

#### 2.2 Improved Treatment

We note that energy loss is a discrete quantum mechanical process. We shall see that for very thin samples, a particle has even a finite probability of traversing the detector with no energy deposition at all.

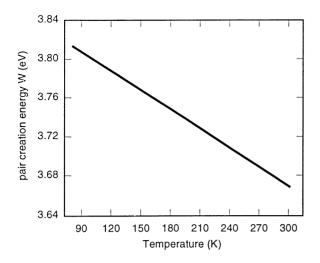

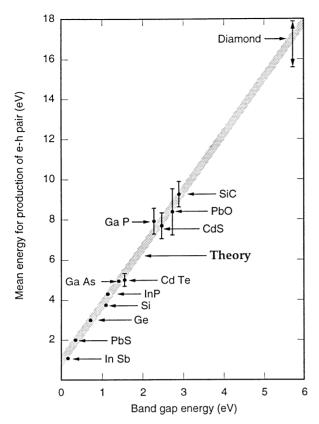

For the low probability close collisions, as noted above, it is valid to consider all atomic electrons as free, and the Rutherford formula applies. Ejected electrons of energies greater than approximately 10 keV will release further atomic electrons along their path. See [3,4] for a detailed treatment. For our purposes, it is sufficient to note that the ultimate products that concern us are electrons, promoted into the conduction band of the material and holes (vacancies in the valence band), and that the generation of each electron-hole pair requires a mean creation energy W of approximately 3.6 eV. The precise value depends weakly on the temperature, see fig. 2, and reflects the temperature dependence of the silicon band gap. Since this is around 1.1 eV, we note that electron-hole generation is a somewhat inefficient process; approximately 2/3 of the energy transferred from the primary (hot) electrons gives rise to phonon generation, eventually appearing as heat in the detector. Beware, this has nothing to do with the non-ionizing energy loss (NIEL) referred to in the introduction to this section! Phonon generation (in contrast to NIEL) is a benign process which does not disrupt the crystal lattice and is usually ignored other than by enthusiasts for bolometric detectors. For our purposes, the  $\delta$ -electrons ejected in close collisions can be considered to generate further electron-hole pairs at a mean rate of one per 3.6 eV of energy loss, *locally* on the track of the projectile, or *distributed* in the case that the  $\delta$ -electron range is significant.

Fig. 2 Temperature dependence of the pair-creation energy W in silicon.

Qualitatively, the effect of the binding of the atomic electrons is to generate resonance-like enhancements in the energy loss cross-section, above the values expected from the Rutherford formula. The K-shell electrons produce an enhancement in the 2 to 10 keV range, the L-shell in the 100 eV to 1 keV range, and the M-shell a resonance at around 20 eV. Below this resonance, the cross-section rapidly falls to zero, in the region around 15 eV where the Rutherford formula would be cut off by the empirical ionization threshold energy.

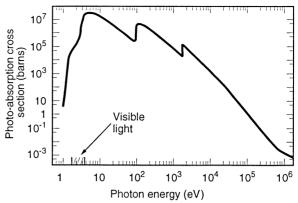

The most satisfactory modern treatment proceeds from the energy-dependent photo-absorption cross-section (a clean point-like process in the terminology of solid state physics). This is of course closely linked to the energy loss process for charged particles, which fundamentally proceeds via the exchange of virtual photons. Combining photo-absorption and EELS (electron energy loss spectroscopy) data, Bichsel [5] has made a precise determination of the MIP energy loss cross-section for silicon. The most subtle effects are connected with the valence (M-shell) electrons. These behave as a nearly homogeneous dense gas (plasma) embedded in a fixed positive charge distribution. The real or virtual photons couple to this by generating longitudinal density oscillations, the quantum of which is called a plasmon and has a mean energy of 17 eV. The plasmons deexcite almost entirely by electron-hole pair creation. These somewhat energetic charge carriers are referred to as 'hot carriers'. Like the  $\delta$ -electrons produced in the close collisions, they lose energy by thermal scattering, optical phonon scattering and ionization. The topic of hot carriers is a major area of research, but for our purposes (as with the  $\delta$ -electrons) we can ignore the details, since the end product that concerns us is again electron-hole pair creation at a rate of one per 3.6 eV of primary energy deposition. Fig. 3 shows the photoabsorption cross-section for silicon. The plasmon excitation is responsible for the extremely large cross-section in the ultra-violet. It is by virtue of the low energy tail of this cross-section in the visible that silicon has its optical sensing applications. The material becomes almost perfectly transparent once the photon energy falls below the 1.1 eV band gap energy.

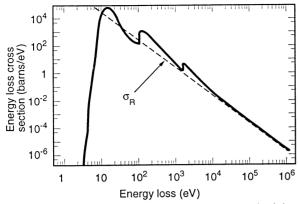

Fig. 4 Energy loss cross-section for minimum-ionizing particles in silicon, versus energy loss in primary collision. Rutherford cross-section  $\sigma_R$  is also plotted.

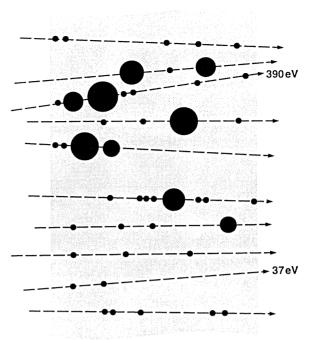

Fig. 5 Monte Carlo calculation of energy deposition in 1  $\mu$ m thick silicon detector. Area of a blob represents the energy deposited in each primary collision process.

The closely related energy loss cross-section for a MIP is show in fig. 4. Note that on average it exceeds the Rutherford cross-section by a factor of several in the energy range 10 eV to 5 keV. Above 10 keV, it is very close to the Rutherford value. By integrating the different components of this cross-section, we can deduce the total mean collision rates associated with the different processes. These are as follows:

| Electrons | Collision probability per micron |

|-----------|----------------------------------|

| K (2)     | $8.8 \times 10^{-3}$             |

| L (8)     | 0.63                             |

| M(4)      | 3.2                              |

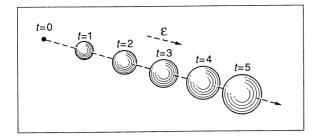

Thus, despite the fact that on average a slice of silicon 1  $\mu$ m in thickness will yield 80 electron-hole pairs, the Poisson statistics on the *primary* process (on average 3.8 collisions per micron) clearly implies a very broad distribution, with even a non-negligible probability of zero collisions, i.e. absolutely no signal. For thin samples, a correct statistical treatment of the primary process is essential if realistic energy loss (straggling) distributions are to be calculated. Their shapes are a strong function of the sample thickness, quite unlike the thickness-independent Landau distribution. The situation is depicted graphically in fig. 5. The area of each circle represents energy loss in a primary collision process. Those of smallest size correspond to plasmon excitation, while the larger ones represent the ionization of L-shell electrons. For these 10 randomly selected tracks, the total energy deposition in the sample ranges from 37 eV to 390 eV.

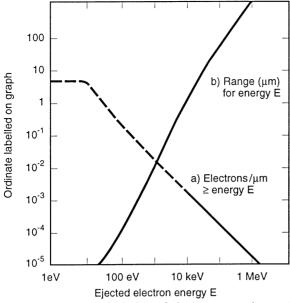

Fig. 6 (a) shows the number of electrons per micron of MIP track above a given energy, and (b) shows the range in silicon corresponding to that energy.

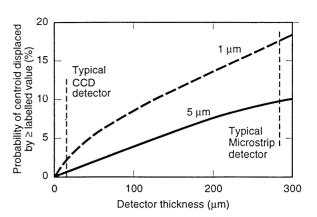

Fig. 7 Detector precision limitations from  $\delta$ -electrons for tracks of normal incidence, as a function of detector thickness.

#### 2.3 Implications for Tracking Detectors

For high precision tracking, there are clear advantages in keeping the silicon detector as thin as possible. A physically thin detector is optimal as regards multiple scattering. A detector with the thinnest possible active region (which may be less than the physical thickness, as we shall see) is optimal as regards point measurement precision, for *two distinct reasons*.

For normal incidence tracks, the concern arises from  $\delta$ -electrons of sufficient range to pull the centroid of the charge deposition significantly off the track. Fig. 6 (a) is an integral distribution of the number of primary electrons per micron of energy greater than a given value, and fig. 6 (b) shows the range of electrons of that energy in silicon. The range becomes significant for high-precision trackers for E greater than approximately 10 keV, for which the generation probability is less than 0.1% per micron. Thus, a detector of thickness 10  $\mu$ m is much less likely to yield a 'bad' co-ordinate than one of thickness 100  $\mu$ m.

If the magnitude of the energy deposition in the detector is measured (by no means always possible) some of the bad co-ordinates will be apparent by the abnormally large associated energy. They could then be eliminated by a cut on the energy deposit, but this usually leads to unacceptable inefficiency and is rarely implemented. The situation is summarised in fig. 7, which indicates the probabilities of the centroid for a track being pulled by more than a certain value (1  $\mu$ m and 5  $\mu$ m) as a function of detector thickness. The advantage of a thin active medium is apparent.

The second reason for preferring detectors to be as thin as possible applies to the case of angled tracks. In principle (and occasionally in practice) it may be possible to infer the position of such a track by measuring the

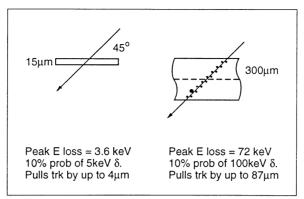

Fig. 8 Effect of energy loss fluctuations on detector precision for angled tracks.

entry and exit points in the detector, but more usually the best one can do is to measure the centroid of the elongated charge distribution, and take this to represent the track position as it traversed the detector mid-plane. In this case, large fluctuations in the energy loss (due to ejection of K- and L-shell electrons and  $\delta$ -electrons) may be sufficient to cause serious track pulls for thick detectors. This is illustrated in fig. 8. In the thin detector there is a 10% probability of producing a  $\delta$ -electron which, if it occurs near one end of the track, pulls the co-ordinate from its true position by 4  $\mu$ m. In the thick detector, there is the same probability of producing a  $\delta$ -electron which can pull the co-ordinate by 87  $\mu$ m.

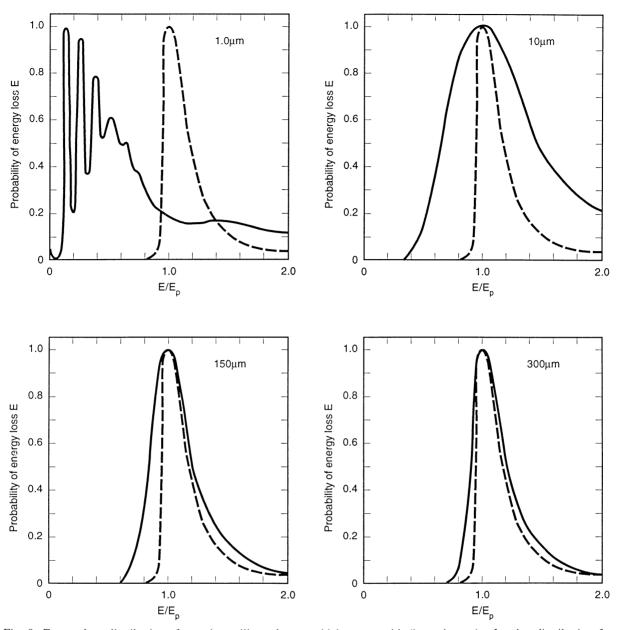

However, our enthusiasm for thin active detector layers must be moderated by the primary requirement of any tracking system, namely a high efficiency per layer. Fig. 9 (based on reference [5]) illustrates the problem we could already anticipate from fig. 5. For very thin detectors (e.g. 1  $\mu$ m Si), we see a very broad energy loss distribution with peaks corresponding to 0, 1, 2, ... plasmons excited, followed by a long tail extending to very large energy losses. An efficient tracking detector could never be built with such an active layer. Even at 10  $\mu$ m silicon thickness, the true distribution is much broader than Landau and has a dangerous low tail. By 300  $\mu$ m, the Landau distribution gives an adequate representation. Thus, while very thin detectors are ideal from the viewpoint of tracking precision, great care must be taken to assure that *system noise* allows a sufficiently *low threshold* to achieve the desired detector efficiency.

#### 2.4 Summary

The valence electrons of silicon are very easily excited into plasmon oscillations from which they dislodge a small number (typically 5) of electrons into the conduction band. A MIP thus creates a fine trail of electron-hole pairs along its track. The quantity W (energy needed to create an electron-hole pair) is approximately 3.6 eV, but depends on the band gap and hence (weakly) on the temperature. This energy loss process allows in principle unprecedented precision (much better than 1  $\mu$ m) compared even to a nuclear emulsion (which needs typically a 400 eV  $\delta$ -electron to blacken a grain). One does need to be prepared to exclude the measurements associated with large energy deposition, but these are rare in thin detectors.

How can this potential performance be achieved in practice? Standard IC processing (the planar technology) provides us with a host of suitable tools. This is after all one of the few areas of engineering in which sub-

Fig. 9 Energy loss distributions for various silicon detector thicknesses, with (in each case) a Landau distribution for comparison. The separate peaks corresponding to 0, 1, 2 ... plasmon excitation are already merged by a thickness of 10  $\mu$ m.

micron tolerances are now standard practice. In Sections 4 and 5, we shall explore some types of detectors currently available. But first we consider some of the basic properties of silicon which allow us in principle to collect and sense the signal charges we have been discussing in this section.

## 3 Physics and Properties of Semiconductors

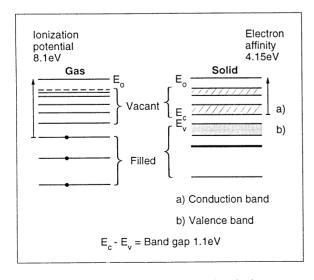

Gaseous silicon has a typical structure of atomic energy levels (see fig. 10). It has an ionization potential of 8.1 eV, i.e. it requires this much energy to release a valence electron, compared with 15.7 eV for argon. As silicon condenses to the crystalline form, the discrete energy levels of the individual atoms merge into a series of energy bands in which the individual states are so closely spaced as to be essentially continuous. The levels previously occupied by the valence electrons develop into the *valence band*, and those previously unoccupied become the *conduction band*. Due to the original energy level structure in gaseous silicon, it turns out that there is a gap between these two bands. In conductors there is no such gap; in semiconductors there is a small gap (1.1 eV in silicon, 0.7 eV in germanium) and in insulators there is a large band gap. In particular, the band gap in silicon dioxide is 9 eV. This makes it an excellent insulator and, coupled with the ease with which the surface of silicon can be oxidised in a controlled manner, accounts partly for the pre-eminence of silicon in producing electronic devices.

We shall denote as  $E_{\rm V}$  and  $E_{\rm C}$  the energy levels of the top of the valence band and the bottom of the conduction band (relative to whatever zero we like to define). The energy needed to raise an electron from  $E_{\rm C}$  to the vacuum  $E_{\rm O}$  is called the electron affinity. For crystalline silicon this is 4.15 eV.

#### 3.1 Conduction in Pure and Doped Silicon

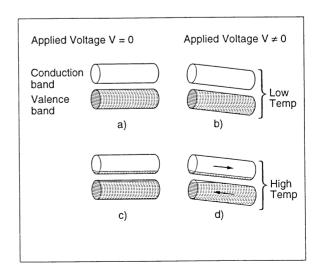

To understand the conduction properties of pure silicon, the *liquid analogy* is helpful. This is illustrated in fig. 11: (a) shows the energy levels in silicon under no applied voltage with the material at absolute zero temperature. All electrons are in the valence band, and under an applied voltage (b) there is no change in the population of occupied states, and so no flow of current; the material acts like an insulator. At a high temperature (c) a small fraction of the electrons are excited into the conduction band, leaving an equal number of vacant states in the valence band. Under an applied voltage (d) the electrons in the conduction band can flow to

Fig. 10 Sketch of allowed energy levels in gaseous silicon which become energy bands in the solid material.

Fig. 11 Liquid analogy for a semiconductor.

the right and there is a re-population of states in the valance band which can be visualised as the left-ward movement of a bubble (holes) in response to the applied voltage.

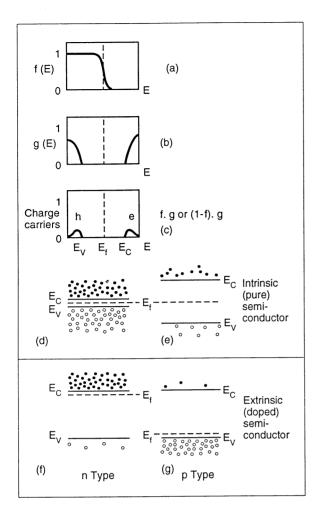

Now kT at room temperature is approximately 0.026 eV. This is small compared with the band gap of 1.1 eV, so the conductivity of pure silicon at room temperature is very low. To make a quantitative evaluation, we need to introduce the Fermi-Dirac distribution function  $f_D(E)$  which expresses the probability that a state of energy E is filled by an electron. Fig. 12 (a) shows the form of this function

$$f_D(E) = \frac{1}{1 + \exp\left(\frac{E - E_f}{kT}\right)}$$

(3.1)

Note that  $E_f$ , the Fermi level, is the energy level for which the occupation probability is 50%. Fig. 12 (b) sketches the density of states g(E) in silicon. The concentration of electrons in the conduction band is given by the product  $f_Dg$ , and the density of holes in the valence band by  $(1-f_D)g$ , as shown in fig. 12 (c). In pure silicon, the Fermi level is approximately at the mid-band gap, and the concentrations of electrons and holes are of course equal. These concentrations, due to the form of  $f_D$ , are much higher in a narrow band gap semiconductor, fig. 12 (d) than in a wide gap material, fig. 12 (e).

So far we have been discussing pure (so-called *intrinsic*) semiconductors. Next we have to consider the *doped* or extrinsic semiconductors. These allow us to achieve high concentrations of free electrons (*n*-type, fig. 12 (f)), or of holes (*p*-type, fig. 12 (g)), by moving the Fermi level very close to the conduction or valence band edge. The procedure for doing this is to replace a tiny proportion of the silicon atoms in the crystal lattice by dopant atoms with a different number of valence electrons.

Fig. 13 shows the lattice structure characteristics of diamond, germanium and silicon crystals. Silicon, with four valence electrons, forms a very stable crystal with covalent bonds at equal angles in space. It is possible (e.g. by ion implantation) to introduce a low level of (for example) pentavalent impurities such as phosphorus. By heating (thermal activation as it is called) the phosphorus atoms can be induced to take up lattice sites in the crystal. For each dopant atom, four of its electrons share in the covalent bonding with neighbouring silicon atoms, but its fifth electron is extremely loosely bound. At room temperature this electron would be free, and hence available for conduction in a sea of fixed positive charge (the phosphorus ions, present at precisely the same average density as the liberated electrons). At absolute zero, all valence electrons would be bound and the phosphorus-doped (n-type) silicon effectively an insulator. The mathematical description of the effect of doping in silicon is to retain the Fermi-Dirac distribution function, but to raise the Fermi level (50% occupation probability) close to the binding energy of the fifth electron, i.e. close to the conduction band edge. The population of those electrons within the conduction band is again given by the overlap of the Fermi-Dirac distribution function (now shifted in energy) and the density of states in the conduction band. Except at very low temperatures (where the Fermi-Dirac function is extremely sharp) the result is a high density of electrons (majority carriers) and a negligible density of holes (minority carriers) in the n-type material in equilibrium, as shown in fig. 12 (f).

Fig. 12 (a) Fermi-Dirac distribution function. The slope increases as the temperature is reduced. (b) Density of states below and above forbidden band gap. (c) Concentration of charge carriers (electrons and holes) available for conduction. (d) and (e) Charge carrier distributions in narrow and wide band gap semiconductors. (f) and (g) Charge carrier distributions in *n*- and *p*-type semiconductors.

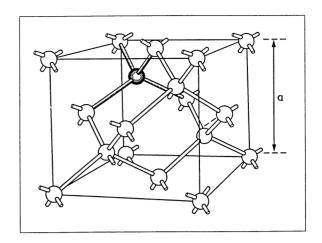

Fig. 13 Lattice structure of diamond, germanium, silicon, etc. where a is the lattice constant.

Alternatively, silicon may be doped with trivalent impurities such as boron. In this case, three strong covalent bonds are formed, but the fourth bond is incomplete. This vacancy (hole) is easily filled by an adjacent electron. Thus, as in the intrinsic material, holes behave as reasonably mobile positively charged carriers in a sea of fixed negative charge (the boron atoms with an additional electron embedded in the fourth covalent bond). The carrier concentrations (now with holes as majority carriers) are give by shifting the Fermi-Dirac distribution to within the hole binding energy i.e. close to the valence band edge as shown in fig. 12 (g).

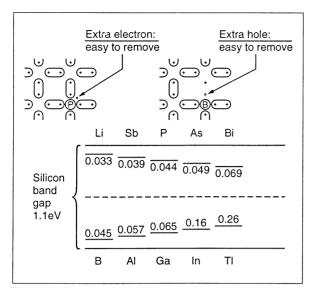

The general situation regarding doped silicon is sketched in fig. 14, which indicates the energy levels corresponding to various commonly used dopant atoms. Pentavalent atoms are referred to as *donors* and trivalent atoms as *acceptors*. Note that the carriers are bound by only approximately 0.045 eV in the common n- and p-type dopants phosphorus and boron, compared to kT at room temperature of 0.026 eV.

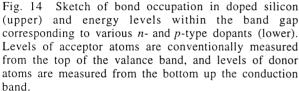

Fig. 15 Electron concentration versus temperature for *n*-type (arsenic doped) silicon. The dashed curve shows the concentration for intrinsic material.

Fig. 15 shows the concentration of electrons in n-type silicon (1.15 x  $10^{16}$  arsenic dopant atoms per cm<sup>3</sup>) as a function of temperature. Below about 100 K one sees the phenomenon of *carrier freeze-out*, loss of conductivitydue to the binding of the donor electrons. This is followed by a wide temperature range over which the electron concentration is constant, followed above 600 K by a further rise as the thermal energy becomes sufficient to add a substantial number of intrinsic electrons to those already provided by the dopant atoms. These will of course be accompanied by an equal concentration of mobile holes. The general behaviour show in fig. 15 is typical of all doped semiconductors.

The *resistivity*  $\rho$  of the material depends not only on the concentration of free holes and electrons but also on their *mobilities*. As one would intuitively expect, the hole mobility is lower than that for electrons. Both depend on temperature and on the impurity concentration. At room temperature, in lightly doped silicon, we have

electron mobility

$$\mu_n = 1350 \text{ cm}^2 \text{ (V s)}^{-1}$$

hole mobility

$$\mu_p = 480 \text{ cm}^2 \text{ (V s)}^{-1}$$

and the resistivity is given by

$$\rho = \frac{1}{q_e(\mu_n.n + \mu_p.p)}$$

(3.2)

[ n and p are the electron and hole concentrations]

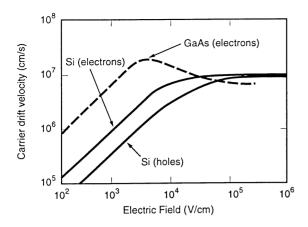

Fig. 16 Carrier drift velocity (electrons and holes) for silicon, and electron velocity for gallium arsenide as function of electric field in the material.

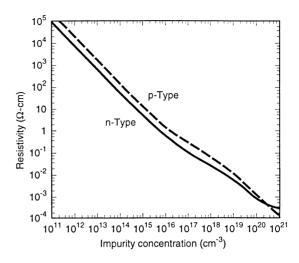

Fig. 17 Resistivity of silicon at room temperature as a function of acceptor or donor impurity concentration.

For pure silicon at room temperature  $n_i = p_i = 1.45 \times 10^{10} \text{ cm}^{-3}$  which gives  $\rho_i = 235 \text{ K}\Omega$  cm.

The carrier drift velocity ( $v_p$  for holes and  $v_n$  for electrons) is related to the mobility by  $v_{p,n} = \mu_{p,n}\mathcal{E}$  where  $\mathcal{E}$  is the electric field strength. This relationship applies only up to a maximum field, beyond which saturation effects come into play and one enters the realm of 'hot carriers' which lose energy by impact ionization (creation of additional electron-hole pairs). Fig. 16 shows the situation for silicon, as well as the fact that nearly ten times higher electron drift velocities are achievable in gallium arsenide, which therefore has the potential for much faster electronic circuits.

The ionization rate is defined as the number of electron-hole pairs created per unit of distance travelled, by an electron or hole. It depends primarily on the ratio  $q_e\mathcal{E}/E_I$  where  $E_I$  is the effective ionization threshold energy, damped by terms reflecting the energy loss of carriers by thermal and optical phonon scattering, see reference [6]. For silicon,  $E_I$  is approximately equal to W (3.6 eV) for electrons and 5.0 eV for holes. The ionization rate becomes significant for electric fields in the range  $10^5$  to  $10^6$  V/cm in silicon, leading to the saturation of carrier drift velocity shown in fig. 16.

The resistivity as a function of dopant concentration is shown in fig. 17. For silicon detectors, as will be explained in the next section, we are often concerned with unusually high resistivity material, some tens of  $K\Omega$  cm. From fig. 17, one sees for example that 20  $K\Omega$  cm p-type material requires a dopant concentration of  $5 \times 10^{11}$  per cm<sup>3</sup>. Remembering that crystalline silicon has  $5 \times 10^{22}$  atoms per cm<sup>3</sup>, this implies an impurity level for the *predominant* impurities of 1 in  $10^{11}$ . Even in the highly developed art of silicon crystal growing, this presents a major challenge. The resistivity noted above in connection with pure silicon (over 200  $K\Omega$  cm) is entirely unattainable in practice. Very high resistivity n-type silicon can be produced in the form of *compensated* material. The most uniformly doped material which can be grown is (for technical reasons) p-type, and this (with a resistivity of about 10  $K\Omega$  cm) is used to start with. It is then turned into n-type material by the procedure known as neutron doping. The crystal is irradiated with slow neutrons and by means of the reaction

$$\mathrm{Si}^{30} + \mathrm{n} \rightarrow \mathrm{Si}^{31}$$

followed by

$$\mathrm{Si}^{31} \rightarrow \mathrm{P}^{31} + \beta^{-} + \overline{\nu}$$

is turned into n-type material. The resistivity is monitored and the irradiation ceases when this, having passed through a maximum, falls to the required value. In this way, material of resistivity as high as 100 K $\Omega$  cm can be made. Achieving reasonable uniformity through the wafer of such a high resistivity is obviously extremely difficult.

We now consider more quantitatively the relationship between the carrier concentration and the Fermi level. The number of conduction band states occupied by electrons is given by

$$n = \int_{E_c}^{E_t} N(E) f_D(E) dE$$

$E_c$  and  $E_t$  are the energy at the bottom and top of the conduction band;  $f_D(E)$  is the function (3.1); N(E), the density of states, is given by the band theory of solids and is proportional to  $(E - E_c)^{1/2}$ . For the commonly encountered situation where Boltzmann statistics applies, for which the Fermi level is at least several times kT below  $E_c$ , the above integral can be approximately evaluated to yield

$$n = N_c \exp\left(-\frac{E_c - E_f}{kT}\right) \tag{3.3}$$

$N_c$  is called the effective density of states. Its meaning is not as intuitively clear as the simple density of states N(E); unlike N(E) it is temperature dependent, being proportional to  $T^{3/2}$ .

The equivalent approximation for the hole concentration is

$$p = N_{\rm v} \exp\left(-\frac{E_f - E_{\rm v}}{kT}\right) \tag{3.4}$$

For *intrinsic* semiconductors, thermal agitation excites electrons from the valence band to the conduction band, leaving an equal number of holes in the valence band. In this case  $n = p = n_i$ , where  $n_i$  is the intrinsic carrier density. There is a dynamic equilibrium between thermal generation on the one hand, and recombination of electrons in the conduction band with holes in the valence band on the other. The neutrality condition obtained by equating (3.3) and 3.4) leads to

$$E_f = E_i = \frac{E_c + E_V}{2} + \frac{kT}{2} \ln \left( \frac{N_V}{N_c} \right)$$

(3.5)

Thus the Fermi level of an intrinsic semiconductor lies very close to the middle of the band gap. The intrinsic carrier density is given from (3.3) and (3.4) also:

$$pn = n_i^2 = N_c N_v \exp(-E_g / kT)$$

(3.6)

where  $E_g = E_C - E_V$

Note that

$$n_i = \sqrt{N_c N_v} \exp(-E_g / 2kT)$$

(3.7)

$\propto T^{3/2} \exp(-E_g / 2kT)$

Thus  $n_i$  has a rapid temperature dependence, doubling for every 12° C rise for silicon around room temperature.

For doped silicon, e.g. n-type, the neutrality condition is between the ionized donors and the conduction band electrons created by the ionization process. For a dopant energy level  $E_d$ , the number of ionized donors is related to the Fermi level by the relation

$$N_d^+ = \frac{N_d}{1 + 2\exp\left(\frac{E_f - E_d}{kT}\right)}$$

(3.8)

See reference [7]. From (3.3) and (3.8) we have the neutrality condition

$$N_c \exp\left(-\frac{E_c - E_f}{kT}\right) = \frac{N_d}{1 + 2\exp\left(\frac{E_f - E_d}{kT}\right)}$$

(3.9)

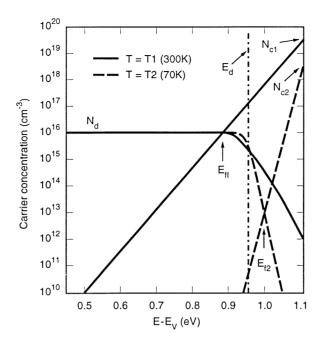

Fig. 18 shows graphically the solution of (3.9) for two temperature values. At room temperature, the donor atoms are completely ionized and the carrier concentration is essentially equal to  $N_d$ , with  $E_f = E_{f1}$  a little below  $E_d$ . At the reduced temperature,  $E_f = E_{f2}$  falls in the small energy range between  $E_d$  and  $E_c$  and the carrier concentration plummets. Conversely, at very high temperatures, thermal excitation of valence band electrons would become dominant, causing the carrier concentration to rise rapidly, and the Fermi level to stabilise near the middle of the band gap, off-scale to the left in the figure.

For p-type material the number of ionized acceptors is given by

$$N_a^- = \frac{N_a}{1 + 4 \exp\left(\frac{E_a - E_f}{kT}\right)}$$

(3.10)

The difference in the factors in the denominator arises from the difference between the ground-state degeneracy for donor and acceptor levels.

Fig. 18 Number of ionized donors and number of conduction band electrons versus the Fermi energy level  $E_f$ .

In general, for doped material we have

$$n = n_i \exp\left(\frac{E_f - E_i}{kT}\right)$$

$$p = n_i \exp\left(\frac{E_i - E_f}{kT}\right)$$

(3.11)

and  $pn = n_i^2 = N_c N_v \exp(-E_g / kT)$  just as for intrinsic material. Thus the deviation of a doped semiconductor from the intrinsic condition can be simply represented by a shift in the Fermi energy level with respect to the intrinsic level. The constancy of the pn product for different doping conditions is a particular example of the very important law of mass action which applies as much in semiconductor theory as it does in chemistry. In thermal equilibrium, the increase in electron concentration by donor doping causes a decrease in the concentration of mobile holes (by recombination) such that the pn product is constant. The ionized donors in this sense are passive bystanders, serving to preserve charge neutrality. It is generally valid to think of n-type material in equilibrium as containing only mobile electrons and p-type material as containing only mobile holes, the majority carriers in each case.

#### 3.2 The pn Junction

We now need to introduce a most important fact related to conducting materials which are electrically in contact with one another and in thermal equilibrium; they all must establish the same Fermi energy. This applies to

metal/semiconductor systems *n*-type/*p*-type systems, etc.

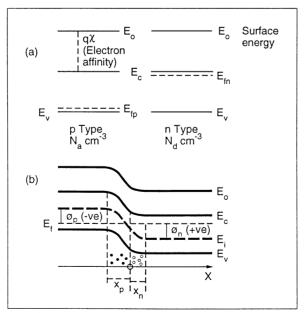

Charge flows from the high to low energy region for that carrier type until this condition is established. For example, at a pn junction there develops a fixed space charge of ionized donors and acceptors, creating a field which opposes further drift of electrons and holes across the junction. The *depletion approximation* says that the semiconductor in this condition changes abruptly from being neutral to being fully depleted. This is far from obvious and in fact there is a finite length (the *Debye length*, typically 0.1  $\mu$ m) over which the transition takes place. But the depletion approximation will be adequate for all the examples we need to consider. Let us look in some detail at the important case of the pn junction. Before contact (fig. 19 (a)) the surface energy  $E_0$  is equal in both samples; the p-type Fermi level is close to  $E_v$  and the sample is densely populated by holes; the n-type Fermi level is close to  $E_c$  and the sample is densely populated by electrons.

On contact, the electrons diffuse into the electron-free material to the left, and the holes diffuse to the right. In so doing the electrons leave exposed donor ions (positively charged) over a thickness  $x_n$  in the n-type material, and the holes leave exposed acceptor ions (negatively charged) over a thickness  $x_p$  in the p-type material. This builds up an electric field which eventually just balances the tendency for current to flow by diffusion. Once this condition is reached (fig. 19 (b)) the Fermi levels in the materials have become equal. The electrical potentials in the two samples (for example the potential energy at the surface  $E_0$  or at the conduction band edge  $E_c$ ) are

Fig. 19 (a) Energy levels in two silicon samples (of *p*-and *n*-type) when electrically isolated from one another. (b) When brought into contact, the Fermi level is constant throughout the material. The band edges bend in accordance with the space charge generated.

now unequal.

Intuitively, this can be understood as follows. Initially, the electrons at a particular level in the conduction band of the n-type material see energy levels in the p-type material at equal or lower energy which are unpopulated, so they diffuse into them. The developing space charge bends the energy bands up, so that these levels become inaccessible. Eventually, only very high energy electrons in the n-type material see anything other than the absence of states of the band gap in the p-type material, and conversely for the holes in the p-type material.

Let us develop this quantitatively, adopting a co-ordinate system in which the pn junction of fig. 19 (b) is at position x = 0.  $E_0$ ,  $E_c$ ,  $E_i$  and  $E_v$  all follow the same x dependence. The zero of the electric potential  $\phi$  is arbitrary, so we define

$$\phi = -\frac{(E_i - E_f)}{q_a} \tag{3.12}$$

Thus

$$\phi$$

is 0 for intrinsic material positive for  $n$ -type negative for  $p$ -type

From (3.11), in the case of fully ionized donors and acceptors,

$$\phi_n = \frac{kT}{q_e} \ln \left( \frac{N_d}{n_i} \right)$$

$$\phi_p = -\frac{kT}{q_e} \ln \left( \frac{N_a}{n_i} \right)$$

The potential barrier

$$\phi_i = \phi_n - \phi_p = \frac{kT}{q_e} \ln \left( \frac{N_d N_a}{n_i^2} \right)$$

(3.13)

Notice that the potential barrier falls linearly with temperature since it is sustained by the thermal energy in the system. We may deduce the electric field strengths  $\mathcal{E}(x)$  near the junction by using Poisson's equation

$$\frac{d^2\phi}{dx^2} = -\frac{d\mathcal{E}}{dx} = -\frac{q_e}{\varepsilon_s}\rho(x)$$

$$\varepsilon_s$$

is the permittivity of silicon  $= \varepsilon_r \varepsilon_0$

$\varepsilon_0$  is the permittivity of space  $= 8.85 \times 10^{-14} \text{ F cm}^{-1}$

$= 55.4 \text{ e}^{-}/\text{V } \mu\text{m}$

$\varepsilon_r$  is the dielectric constant or relative permittivity of silicon = 11.7

For

$$x_n \ge x \ge 0$$

For

$$-x_p \le x \le 0$$

$$\frac{d\mathcal{E}}{dx} = +\frac{q_e N_d}{\varepsilon_s} \qquad \therefore \mathcal{E}(x) = -\frac{q_e N_d}{\varepsilon_s} (x_n - x)$$

$$\frac{d\mathcal{E}}{dx} = -\frac{q_e N_a}{\varepsilon_s} \qquad \therefore \mathcal{E}(x) = -\frac{q_e N_a}{\varepsilon_s} (x + x_p)$$

$$(3.14)$$

The *undepleted* silicon on either side of the junction is *field-free*. The depleted silicon close to the junction experiences an electric field whose strength is maximal at the junction and is directed always to the left, i.e. opposing the flow of holes to the right and opposing the flow of electrons to the left.

Requiring continuity of the field strength at x = 0 implies

$$N_a x_p = N_d x_n \tag{3.15}$$

Thus, if one wants to make a deep depletion region on one side of the junction (important, as we shall see, for many detectors) we need to have a very low dopant concentration, i.e. very high resistivity material.

The electric field strength varies linearly with x; the electric potential, by integration of (3.14), varies quadratically.

For

$$x_n \ge x \ge 0$$

$$\phi(x) = \phi_n - \frac{q_e N_d}{2\varepsilon_s} (x_n - x)^2$$

For  $-x_p \le x \le 0$

$$\phi(x) = \phi_p + \frac{q_e N_a}{2\varepsilon_s} (x + x_p)^2$$

(3.16)

Requiring continuity of the potential at x = 0 implies

$$x_n + x_p = \left[ \frac{2\varepsilon_s}{q_e} \phi_i \left( \frac{1}{N_a} + \frac{1}{N_d} \right) \right]^{1/2}$$

(3.17)

From (3.13)  $\phi_i$  depends only weakly on  $N_a$  and  $N_d$ .

If, for example,  $N_a >> N_d$  we have  $x_p \approx 0$  and (3.17) gives  $x_n \propto N_d^{-1/2}$ .

So a factor two increase in resistivity leads to a factor of only  $\sqrt{2}$  increase in depletion depth.

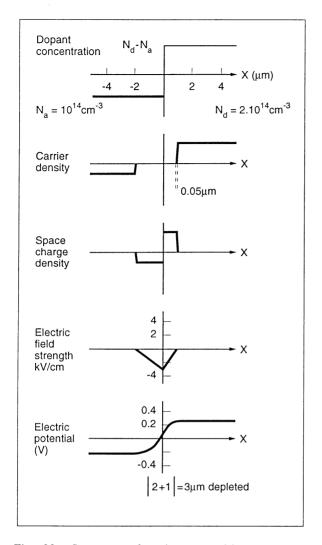

Fig. 20 summaries these results on the characteristics of an unbiased pn junction, with the inclusion of some typical numerical values based on  $N_a = 10^{14} \, \text{cm}^{-3}$  and  $N_d = 2 \times 10^{14} \, \text{cm}^{-3}$ . The peak field in this case is about 3 kV/cm.

Fig. 20 Summary of various quantities across an unbiased pn junction.

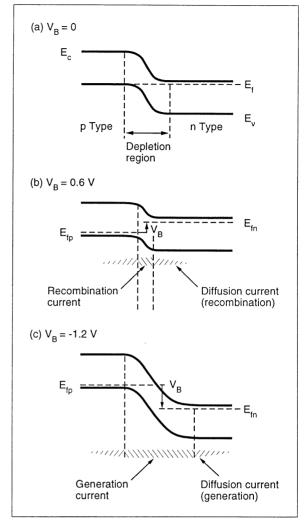

Fig. 21 Effect of an applied voltage across the semiconductor junction.

We now consider the effect of applying a voltage across the junction. Under equilibrium conditions, electronhole pairs are continually generated by thermal excitation throughout the semiconductor. In the case of zero bias (fig. 21 (a)) the electrons and holes generated within the bulk of the semiconductor recombine. Those generated in the depletion region are swept into the undepleted silicon, holes to the left, electrons to the right. This effect would act to reduce the potential barrier and so is compensated by a small flow of *majority carriers* which find themselves with just sufficient energy to diffuse across the barrier in the opposite directions at just the rate needed to cancel the charge generation in the depleted material. The overall effect is of zero current flow, i.e. equilibrium.

By applying a forward bias (fig. 21 (b)) we separate the previously equal Fermi levels by an amount equal to the bias voltage; the system is no longer in thermal equilibrium or this condition could not be maintained. Although there is still an electric field in the depletion region which is directed against the current flow, the depletion region is narrowed and the potential barrier is now inadequate to prevent majority carriers from flooding across it, holes from the left and electrons from the right. Many of these will recombine within the depletion region giving rise to the *recombination current*. Those which survive are absorbed within one or two diffusion

Fig. 22 Operating principles of a simple microstrip detector. It consists essentially of a reverse biased diode, operated at a voltage sufficient to fully deplete the thick, high resistivity, *n*-layer.

lengths by recombination with the majority carriers on that side of the junction, giving rise to the *diffusion* current. Beyond these regions there is just a steady flow of majority carriers supplied from the voltage source to keep the current flowing. Notice that in a forward biased junction the current flow results entirely in electronhole recombination.

With a reverse bias, we have the situation shown in fig. 21 (c). The depletion region is now much wider and electron-hole pairs generated within it are efficiently swept into the undepleted silicon, electrons to the right and holes to the left, giving rise to the *generation current*.

Unlike the case of the unbiased junction, there is now no supply of majority carriers able to overcome the increased potential barrier across the junction. On the contrary, the thermal generation of *minority carriers* within one or two diffusion lengths of the depletion region leads to some holes generated in the *n*-region reaching this depletion region and then being briskly transported across it, and conversely for electrons generated in the *p*-region. This leads to the so-called *diffusion current*. In the case of the reverse-biased junction, the current flow is thus caused entirely by electron-hole *generation*. The current flow across reverse-biased junctions is of great importance in determining the noise limits in silicon detectors. An immediate observation is that, since this current arises from *thermal* generation of electron-hole pairs, the operating temperature will be an important parameter.

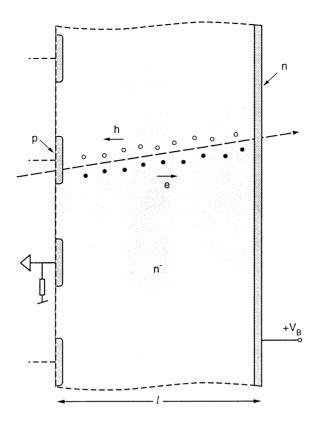

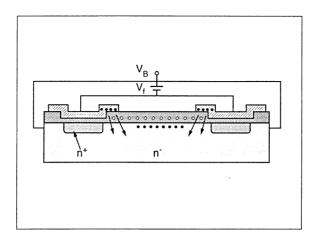

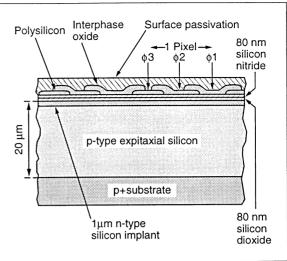

Before continuing to discuss this point, it is worth noting that we have finally collected up enough information to calculate the characteristics of a typical particle detector, and it is instructive to do so. Referring to fig. 22, we have a silicon detector of thickness  $\ell$  made of good quality, high resistivity n-type silicon ( $\rho = 10 \text{ K}\Omega \text{ cm}$ ). On the front surface we make shallow implants of acceptor atoms (the p-strips) and on the back surface we make a highly doped n-type implant to provide a good low-resistance ohmic contact. The terms  $n^+$  and  $p^+$  are conventionally used to represent high doping levels, n and p represent moderate levels,  $n^-$ ,  $p^-$  or  $p^-$  and  $p^-$  are conventionally used to represent high doping levels,  $p^-$  and  $p^-$  represent low levels, and  $p^-$  is used for intrinsic or compensated material of the highest possible resistivity.

Now we apply a positive voltage  $V_B$  to the *n*-type surface with the aim of completely depleting the detector. In this way we shall ensure complete collection of the electrons and holes generated by the passage of a charged particle; with incomplete depletion we would lose signal by recombination. Equation (3.17) applies, with the difference that we replace  $\phi_i$  by  $V_B + \phi_i$  since the junction is biased in the direction which assists the previously existing depletion voltage.

We have

$$\begin{aligned} x_n + x_p &\approx x_n = \left[ \frac{2\varepsilon_s}{q_e} \left( V_B + \phi_i \right) \left( \frac{1}{N_a} + \frac{1}{N_d} \right) \right]^{1/2} \\ &\approx \left[ \frac{2\varepsilon_s}{q_e} \times \frac{V_B}{N_d} \right]^{1/2} \end{aligned}$$

From fig. 17, we see that  $N_d \approx \frac{6 \times 10^{15}}{\rho}$  and we require  $x_n = \ell$

$$\therefore V_B = \frac{q_e}{2\varepsilon_s} \times \frac{6 \times 10^{15}}{\rho} \times \ell^2$$

$$= \frac{10^{-4}}{2 \times 55.4 \times 11.7} \times \frac{6 \times 10^{15}}{\rho} \ell^2 \times 10^{-8}$$

where  $\ell$  is in  $\mu$ m and  $\rho$  in  $\Omega$  cm

$$\therefore V_B = \frac{4.63 \ \ell^2}{\rho}$$

For the above example,  $V_B = 42 \text{ V}$  is the potential needed to fully deplete the detector. We also find  $\mathcal{E}_{\text{max}} = 2.8 \text{ kV/mm}$ . This looks comfortable in terms of the breakdown field in silicon. However, in a real detector, it is important to pay attention to the regions near the edges of the *p*-strips, where the fields can be very much higher.

Returning to the general properties of the reverse biased junction, the most important parameter influencing the leakage current is the operating temperature. At high temperatures, above 100 °C typically, the leakage current

is dominated by thermal electron-hole generation within approximately one diffusion length of the depletion edge. The diffusion length for minority carriers is

$$L_D = \sqrt{D\tau_m} \tag{3.18}$$

where D is the diffusion constant and is related to the mobility  $\mu$  by the Einstein relation

$$D = \frac{kT}{g_a} \mu \tag{3.19}$$

For electrons

$$D_n = 34.6 \text{ cm}^2 \text{ s}^{-1}$$

For holes  $D_p = 12.3 \text{ cm}^2 \text{ s}^{-1}$  at room temperature

$\tau_m$  is the minority carrier lifetime, and it can vary from about 100 ns to more than 1 ms depending on the quality of the silicon. This point will be discussed further. This leakage current (termed the diffusion current, as previously noted) depends only weakly on the reverse bias voltage, but is highly temperature dependent due to its origin in the thermal generation of minority carriers.

At lower temperatures (less than about  $100^{\circ}$ C) the diffusion current becomes negligible and the generation current dominates. This continues to show a similarly fast temperature dependence, but is now also quite voltage dependent, since the depletion width is proportional to  $V_B^{1/2}$ .

The diffusion and generation currents depend on the rate of generation of electron-hole pairs, and the diffusion current depends also on the minority carrier lifetime. These quantities are in fact closely related. Direct thermal generation of an electron-hole pair is quite rare in silicon for reasons which depend on the details of the crystal structure. Most generation occurs by means of intermediate generation-recombination centres (impurities and lattice defects) near the band gap centre. Thus an electron-hole pair may be thermally created in a process where the hole is released into the valence band and the electron is captured by the trapping centre in one step, to be subsequently emitted into the conduction band. These bulk trapping states vary enormously in their density and can be held down to a low level by suitable processing. It is precisely these states which determine the minority carrier lifetime already mentioned. Reducing the density of bulk trapping states does two things. It cuts down the thermal generation of charge carrier pairs in the material, so reducing the concentration of minority carriers available for the generation of current across a reverse-biased junction. It also increases the minority carrier lifetime and so the diffusion length (but only at  $\tau^{1/2}$ ). The first effect vastly outweighs the second, so that a low density of bulk trapping states is highly advantageous in ensuring low leakage current. As we shall see later, even originally high grade silicon can deteriorate due to the production of bulk trapping states by radiation damage. Mid-band gap impurities such as gold are a particularly serious source of bulk trapping centres. Even in low concentrations, gold atoms strongly reduce the carrier lifetimes, and lead to greatly increased leakage current.

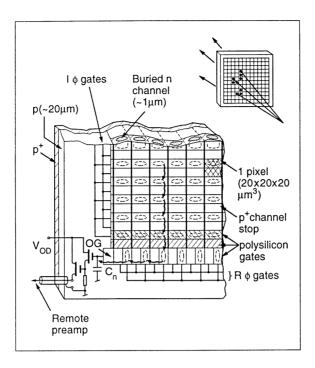

These effects are less serious in cases where one is collecting large signals promptly. But in cases of small signals and/or long storage times (such as in a silicon drift chamber, or CCD), particular care is needed. One important design criterion is to keep the stored charges well away from the surface of the silicon, since the silicon/silicon dioxide interface always has a high level of lattice defects. This criterion has led to the development of various forms of *buried channel* radiation detectors, to be discussed later.

#### 3.3 Charge Carrier Transport in Silicon Detectors

While the charge generated by an ionizing particle is being transported by the internal field in the detector, the process of diffusion spreads out the original very fine column of charge. In the case of very highly ionizing particles (such as alphas) the original density of electrons and holes can be so high that space-charge effects are important. In the case of MIPs, however, such effects are negligible and the time development of the electron and hole charge distributions may be treated by simple diffusion theory.

Consider a local region of electron charge, for example a short section of the particle track length within the silicon. Under the influence of the internal field, this will be drifted through the material and at the same time will diffuse radially as indicated in fig. 23.

The RMS radius of the charge distribution increases as the square root of drift time  $t_d$ , as in (3.18), with standard deviation  $\sigma = \sqrt{2Dt_d}$ . Thus 50% of the charge is contained within a radius of 0.95  $\sqrt{Dt_d}$ . Assuming a 'typical' drift field in depleted silicon of 1 kV/cm, and using the fact that the drift velocity  $v_n = \mu_n \mathcal{E}$ , we obtain the following indication of the growth of a charge packet with time:

| Drift Time | Charge Radius      | Drift Distance |

|------------|--------------------|----------------|

| 10 ns      | 6 μm               | 135 μm         |

| 1 μs       | $60~\mu\mathrm{m}$ | 14 mm          |

Diffusive charge spreading is an attractive option for improving spatial precision beyond the limits of the detector granularity. For example, one might hope to achieve precision of one or two microns from a strip detector with 25  $\mu$ m pitch, by centroid finding on the basis of measured charge collection in adjacent strips. This depends on achieving a charge radius of  $\geq 30~\mu$ m which (from the above table) implies large drift distances and/or gentle drift fields. Ideas for improved precision by centroid finding may be limited by the available resistivity of silicon.

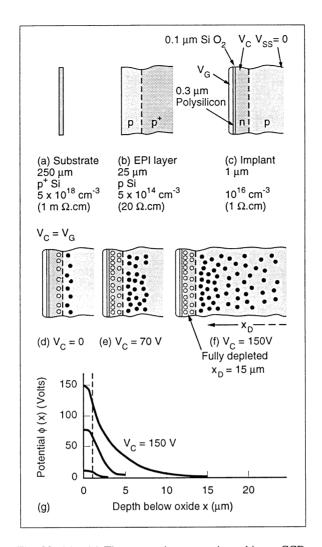

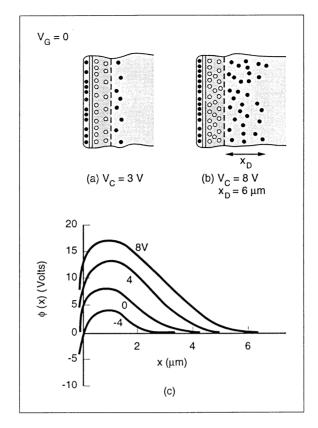

There is however, an alternative approach that has so far been applied only to CCD detectors, but which could be of more general interest. A wafer cut from a silicon crystal will normally have a rather uniform dopant concentration. It is possible subsequently to grow relatively thick (up to around 100  $\mu$ m) *epitaxial layers* on the substrate wafer, of excellent crystalline quality and quite different (but also uniform) dopant concentration. For detector applications, a low resistivity substrate with a high resistivity epi layer is of particular interest. In the CCD case, as we shall see, the epi layer would be implanted with an *n*-layer, and biased so as to deplete only approximately 3  $\mu$ m depth. The charge carrier transport associated with (for example) a charged particle track

Fig. 23 Combined drift and diffusion of an initially compact charge cluster (electrons or holes) as a function of time over equal time intervals.

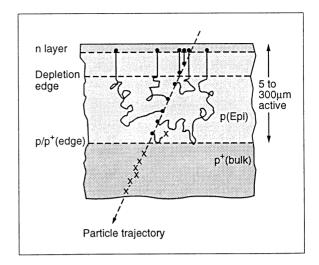

Fig. 24 Charge collection from a silicon structure as used in some pixel devices.

traversing such a structure is depicted in fig. 24. Electrons within the thin depletion region are promptly collected into the buried channel, with no time for lateral diffusion. Electrons from the highly doped  $p^+$  bulk are completely disposed of by recombination (very short minority carrier diffusion length in this material). However, electrons generated in the undepleted epitaxial layer find themselves able to diffuse homogeneously in all directions. Those which approach the  $p/p^+$  junction experience a potential barrier as we have already discussed in the case of the unbiased pn junction, of magnitude

$$\phi_B = \frac{kT}{q_e} \ln \left( \frac{N_{p^+}}{N_p} \right)$$

For a 20  $\Omega$  cm epi layer on a highly doped 0.1  $\Omega$  cm substrate, we find

$$\phi_B = 180 \text{ mV}$$

compared with  $\frac{kT}{q_e} = 26 \text{ mV}$

at 300 K. The  $p/p^+$  interface therefore acts as a *perfect mirror*, and the electrons continue diffusing until they happen to approach the pn depletion edge, at which point they are stored. Thus a MIP leaves an electron charge cluster which is transversely spread by an amount related to the epi layer thickness. Such a detector made with partially undepleted thick-epi material is in principle better for precision tracking by centroid finding than a fully depleted detector. To fully exploit this concept, one has to pay attention to the detector granularity, epi layer thickness, readout noise, etc. The most spectacular results in precision centroid finding in CCDs have been obtained not as yet with MIPs but with defocused star images in satellite guidance system, where precision below 0.1  $\mu$ m has been achieved using 20  $\mu$ m pixels. This constitutes a very important demonstration of the inherent pixel-to-pixel homogeneity possible with high quality silicon processing.

#### 4 Microstrip Detectors

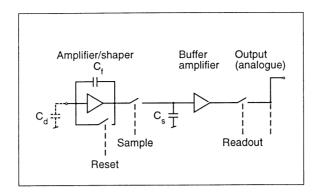

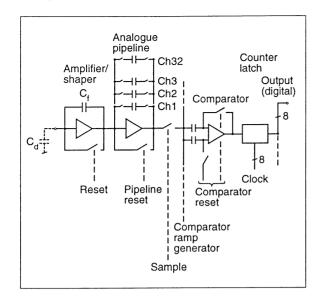

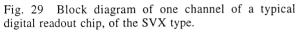

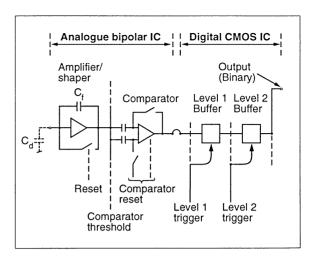

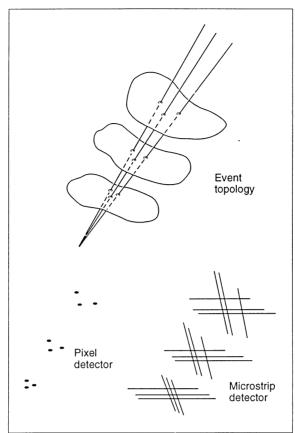

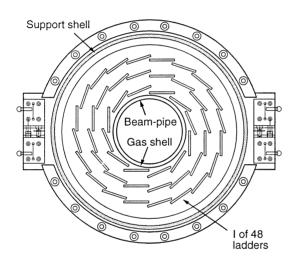

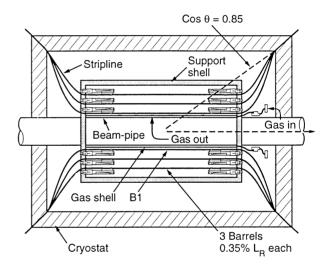

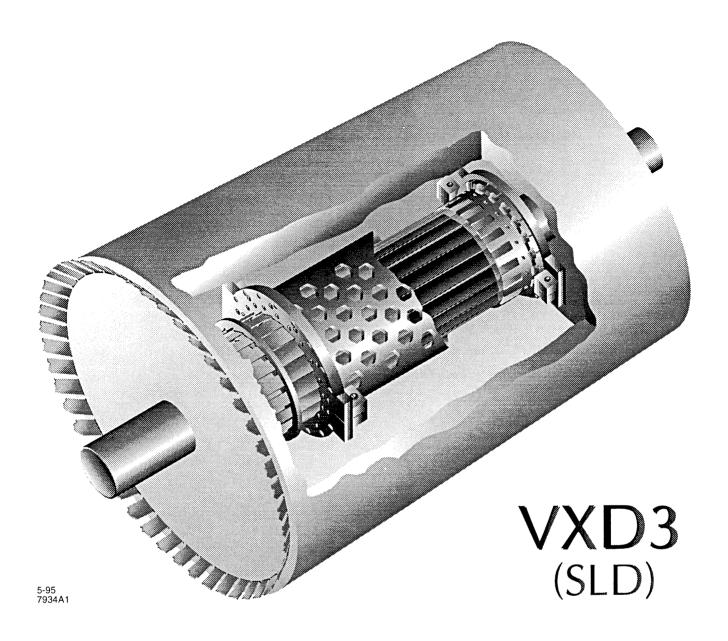

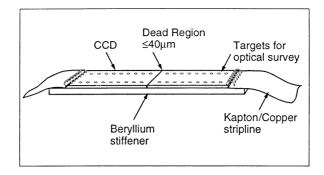

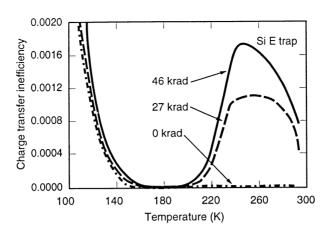

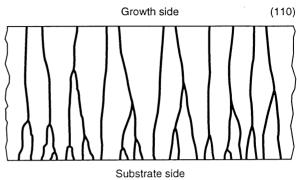

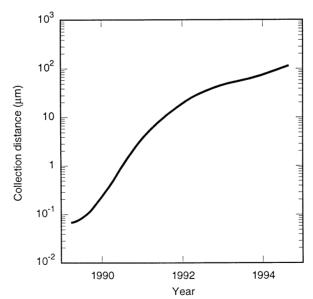

#### 4.1 Introduction