# LCFI Research & Development Programme, Results and Plans

- Minimising the material budget.

- Operating CCDs at the LC.

- Radiation damage.

- Readout speed.

- Future R&D programme.

- Summary and request to PPESP.

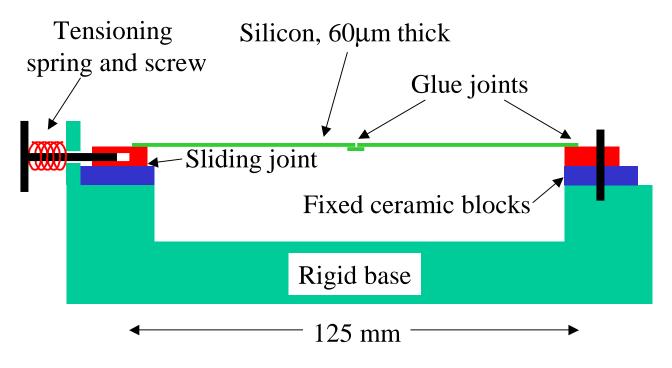

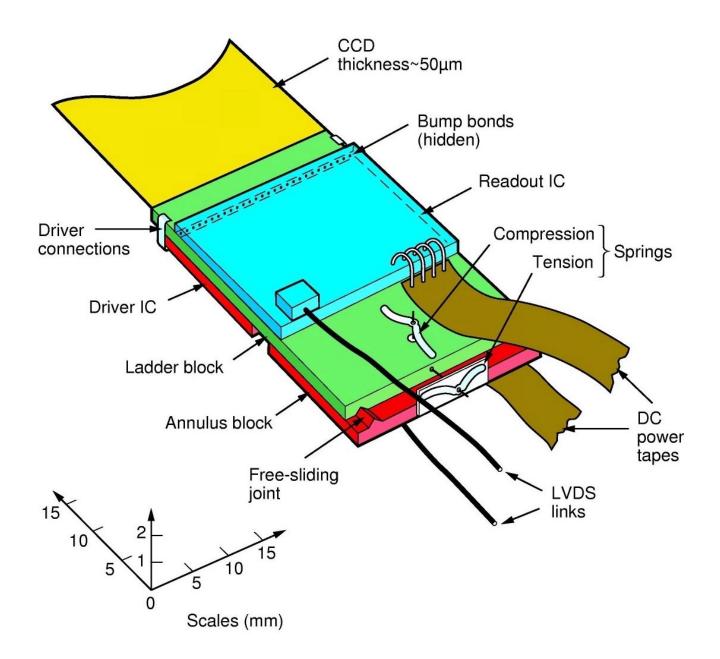

- Hold CCDs at ends, under tension.

- Particles see 60  $\mu$ m of Si (0.06% X<sub>0</sub>).

- C.f. world record of 0.4% X<sub>0</sub> to date (SLD vertex detector).

- Stability under temperature cycling?

- Schematic diagram of test rig:

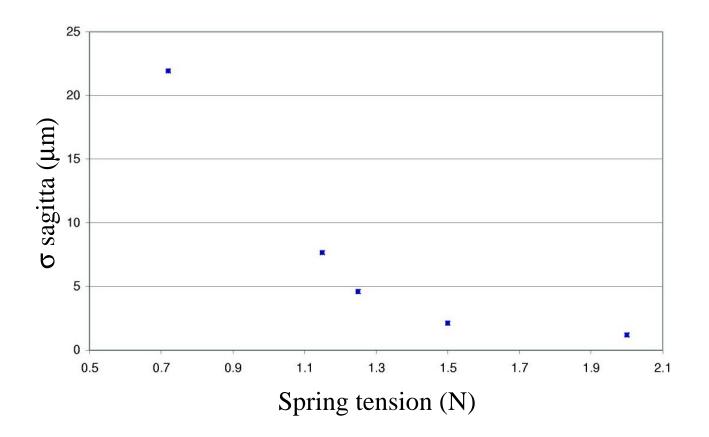

• For various tensions, repeatedly disturb, measure sagitta using ATLAS SmartScope.

• Unsupported Si test rig.

• Detail of Si tensioning mechanism.

• Results:

• First studies show  $\sigma \sim 3 \ \mu m$  for tension > 1.5 N.

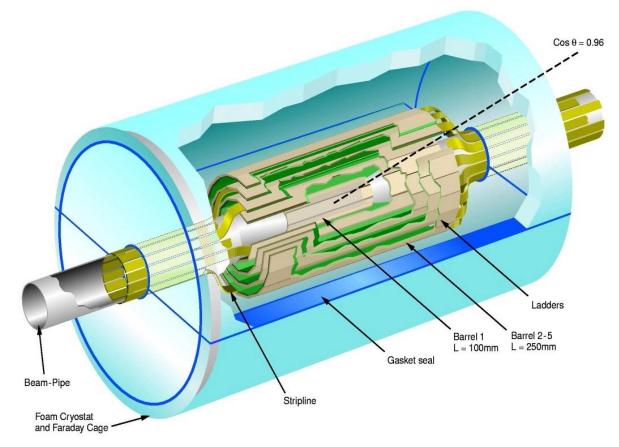

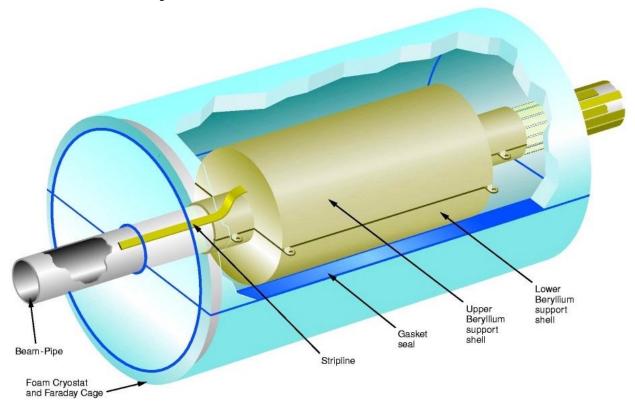

# Unsupported CCDs, VXD design

• Maintain gains achieved by very thin CCD layers.

- Be shell outside inner tracking volume, thickness 1...2 mm.

- Beampipe thickness ~ 0.25 mm Be (0.07% X<sub>0</sub>).

# Surveying CCD ladders

- Two metrology systems:

- Upgraded Oxford ATLAS WhIPM system.

- RAL ATLAS Smartscope.

- Portable LN<sub>2</sub> cryostat for use on either system, study thermal distortions.

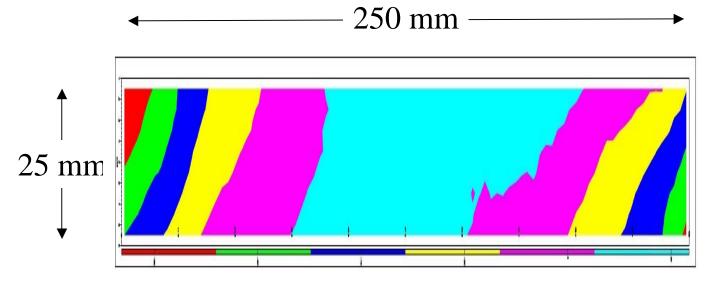

- WHiPM profile of dummy ladder (contours at 20 µm intervals, resolution better than 5µm):

#### Surveying CCD ladders

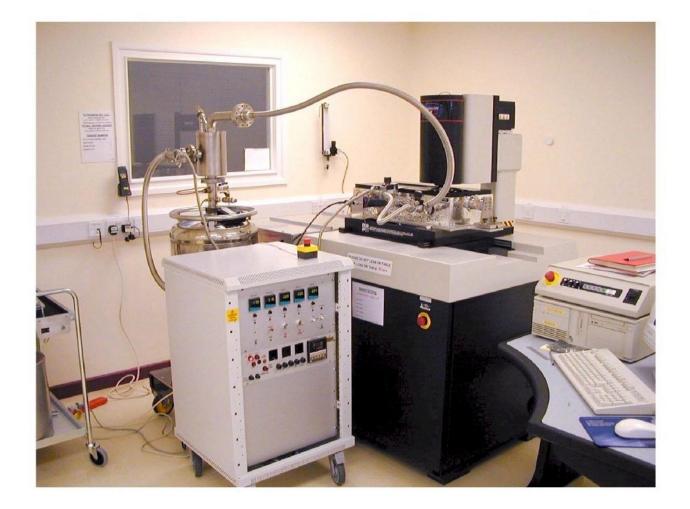

• Cryostat with cooling system on SmartScope at RAL.

# Operating CCDs at the LC: radiation damage

- Neutron dose at LC ~ 4 x 10<sup>8</sup> 1 MeV equivalent n/cm<sup>2</sup> and year.

- Conventional CCDs can tolerate 8...1500 x 10<sup>9</sup> 1 MeV n/cm<sup>2</sup> before CTI drops to 5 x 10<sup>-5</sup>.

- Column parallel CCDs less sensitive.

- Liquid He/N<sub>2</sub> cryostat constructed at Liverpool with optical charge injection.

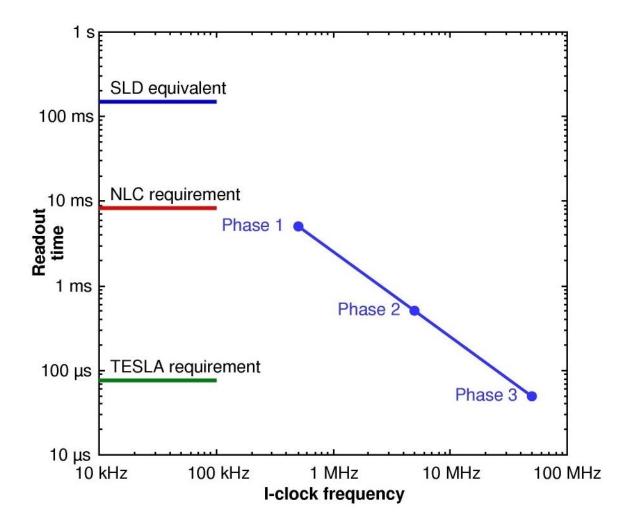

# Operating CCDs at the LC: readout speed

• Major concern here e<sup>+</sup>e<sup>-</sup> pair production.

|                                                                     | NLC    | TESLA    |

|---------------------------------------------------------------------|--------|----------|

| $\sqrt{s}$ (TeV)                                                    | 0.31.0 | 0.090.8  |

| $\mathcal{L}$ (x10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> ) | 0.53.4 | 3.45.0   |

| Rep. Rate (Hz)                                                      | 120    | 53       |

| Bunches/pulse                                                       | 95190  | 28204500 |

| Bunch sep. (ns)                                                     | 2.81.4 | 337189   |

| Radius (cm)                                                         | 1.2    | 1.5      |

| Hits (mm <sup>-2</sup> BC <sup>-1</sup> )                           | 0.03   | 0.03     |

| Hits (mm <sup>-2</sup> BT <sup>-1</sup> )                           | 4      | 80       |

- Must readout TESLA CCDs 10 times per BT to keep occupancy at ~ 4 hits mm<sup>-2</sup>.

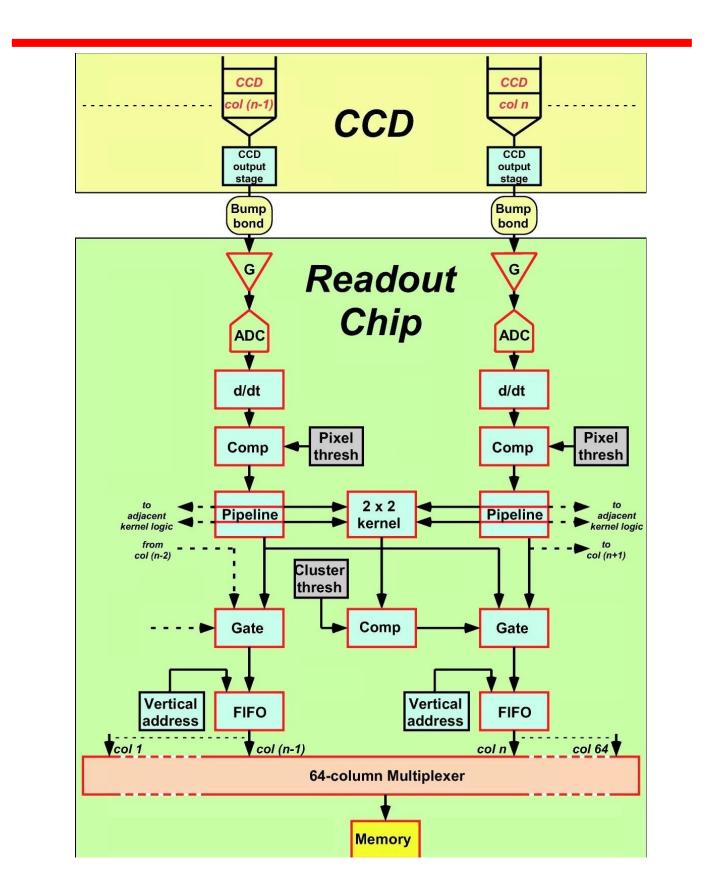

- Need column parallel readout at 50 MHz.

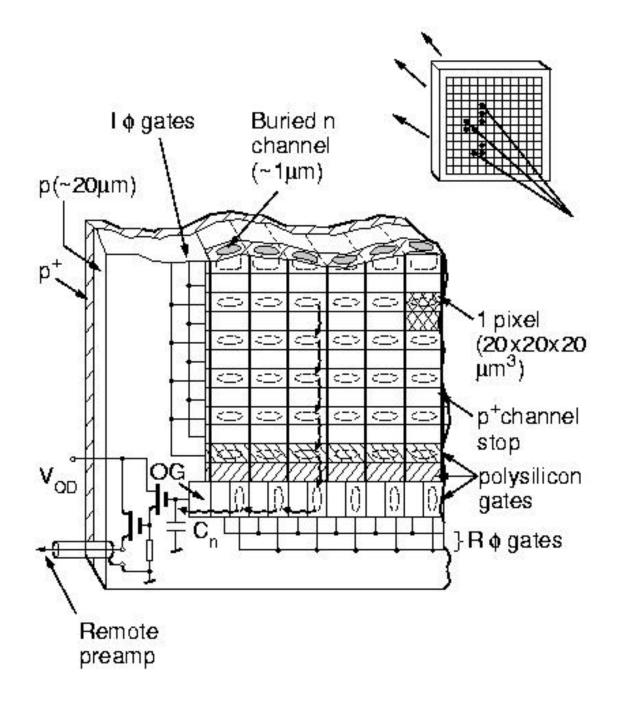

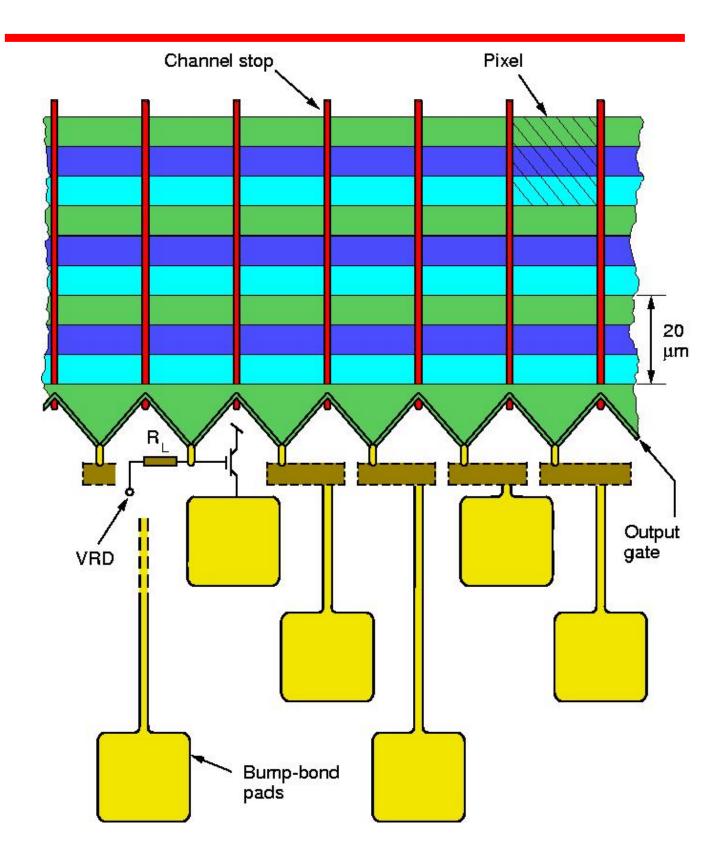

#### Conventional CCD

#### Column parallel CCD

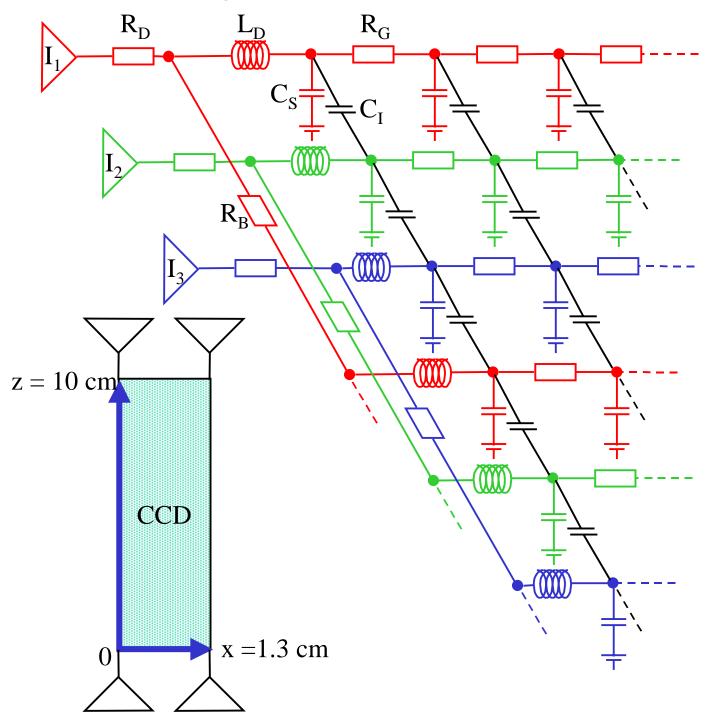

#### SPICE model, inner barrel CCD

• Can the I gates be clocked at 50MHz?

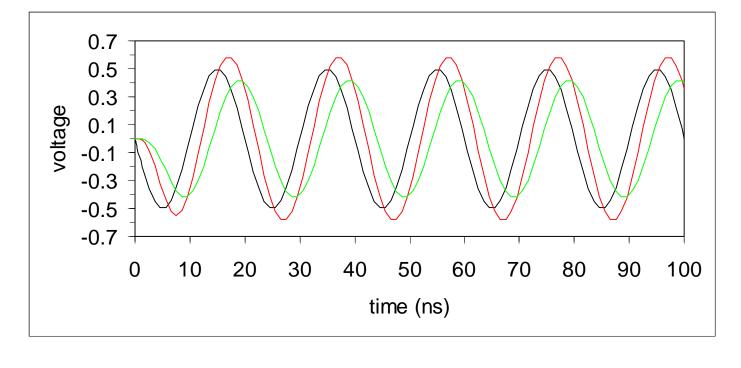

#### SPICE simulation results

- Reduce gate resistance by addition of 1 μm thick 3 μm wide Al strips.

- Reduce bus line resistance by increasing thickness of Al.

- Try 2-phase sinusoidal drive pulses.

# SPICE simulation results

- Waveforms in centre of CCD adequate for efficient operation.

- Total power dissipation/CCD (continuous operation) ~ 4 W.

- TESLA duty cycle ~ 1/200 and outer CCDs can be clocked at lower frequency.

- Total VXD power consumption is few watts.

- Cooling can be achieved with gentle gas flow.

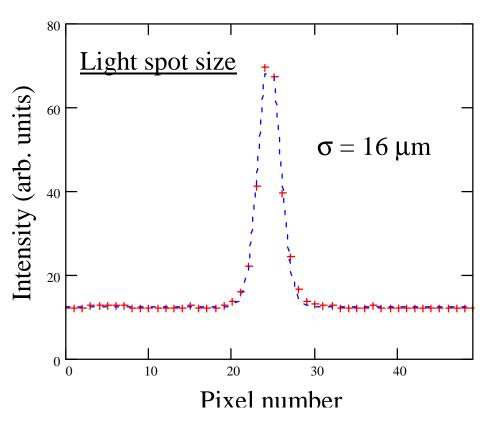

# Experimental studies of readout

- VME based 50 MHz drive and readout electronics designed and under construction.

- CCD58 on motherboard delivered by Marconi.

• First tests imminent.

#### Future R&D

• Three phase programme proposed:

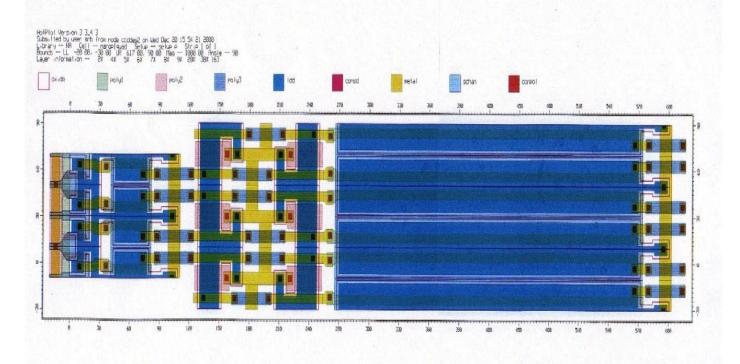

# Future R&D, phase 1

- Move to column parallel readout, but with standard clock frequencies and voltages.

- Main challenge is production of output circuits on pitch of 20 µm.

- Marconi designed possible output circuit following discussions with LCFI.

#### Detail of ladder end

#### Readout logic

#### Future R&D, phases 2 and 3

- Increase readout speed by factor 100 in two steps.

- These steps will depend on results obtained in phase one, but 50 MHz operation requires:

- Metal buttressing.

- Reduced clock voltages.

- Marconi have proposals for achieving above.

- Guide developments and experimental studies using simulations.

- Semiconductor devices modelling group at RAL.

- ISE TCAD at Liverpool.

# CCD modelling

- First task:

- Must understand CCD L, C and R for 50 MHz operation.

- C and R known.

- Simulation of CCD needed to find L.

- Develop test structures to measure L.

- Later:

- Produce full 3D simulation of minimum ionising particle charge collection and transfer in 4 T magnetic field.

#### Summary of progress to date

- The LCFI collaboration has made significant progress in the last two years:

- The VXD design goals are now clear.

- Test rigs are now available.

- 50 MHz capable drive and readout electronics are available, with final systems expected within months.

- First CCDs obtained from Marconi.

- Simulation studies advancing.

- Unsupported silicon tests successful.

#### Future plans

- A three phase and four year programme has been developed which will provide:

- Studies of LC physics involving flavour identification.

- Column parallel CCDs meeting the specifications necessary for the NLC and TESLA.

- Thin unsupported CCD ladder structures.

- High speed readout and driver chips.

- These developments will be useful for SR imaging, space-based applications and time resolved spectroscopy in addition to HEP.